英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

在单个FPGA器件上实现100ps分辨率的内插时间计数器

摘要

本文介绍了一种集成在单片现场可编程门阵列(FPGA)器件上的内插时间计数器的逻辑和性能。由于新设计的用于精确时间到数字转换的FPGA延迟线,以及采用增强型CMOS-FPGA技术,获得了100ps(LSB)的分辨率。通过软件校正延迟线的非线性,将最坏情况下的随机误差170ps降低到70ps。计数器可以测量0-43秒的时间间隔和200兆赫的频率。计数器芯片的最大功耗为260mw。

关键词:索引项延迟电路,现场可编程门阵列,时间计数器,时域测量,时间到数字转换器。

- 导言

在激光测距系统和数字集成电路动态参数测试仪等许多应用中,都需要对时间间隔进行精确测量。这么多年来,能实现皮秒分辨率的主要方法,要么是基于模拟时间的拉伸原理,要么是基于时幅的转换,然后是模数转换器[1]–[5]。这两种方法都与nutt[6]toofferresolution(LSB)ashighas1ps[2]设计的常用插值方法相结合起来,但付出的代价是转换时间长,电路复杂度大大提高高,而且稳定性十分有限。随着电子技术的快速发展,其使得基于直接编码时间的数字延迟线的完全集成时间到数字转换器得到了快速的发展[7]–[11]。这种方法转换的时间非常短,但其比获得高分辨率要困难得多。Mantyniemi这些人提出的双内插计数器的智能设计实现了迄今为止的最佳分辨率(其大约100ps)。[11] 众所周知,这种计数器被设计成在亚微米CMOS工艺中制造的ASIC芯片,其价格昂贵,而且特别是在小批量生产的情况下更突出这一缺点。由于周转时间长(TAT)和需要多次修改,设计过程非常复杂而且周期漫长。从这个角度来看,使用这种廉价的可编程逻辑看起来是很有前途。

最近我们去描述了在单个现场可编程门阵列(FPGA:其采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable LogicCLB(Configurable LogicBlock)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件CPLD即复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。)相比,FPGA具有不同的结构。FPGA利用小型查找表(16times;1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。)芯片上实现的分辨率为200ps、测量范围为43s的内插时间计数器。该计数器是在一个由QuickLogicreg;在m2层CMOS工艺中制造的pASIC1系列一次性可编程器件上实现的。对于下面描述的新设计,我们使用了新的pASIC2家族的FPGA器件,采用3层CMOS工艺制造。新设备提供更短的延迟和改进非常多的逻辑块架构。

(1999年11月10日收到的手稿;2000年3月27日修订。这项工作由波兰科学委员会(KBN)根据合同8T11b02914提供支持。作者来自波兰华沙49号00-908军事科技大学(电子邮件:rszplet@e e.oulo.fi;RSzymanowski@wel.wat.waw.pl)。发布者项目标识符S 0018-9456(00)06354-3)

二 FPGA延迟单元的设计

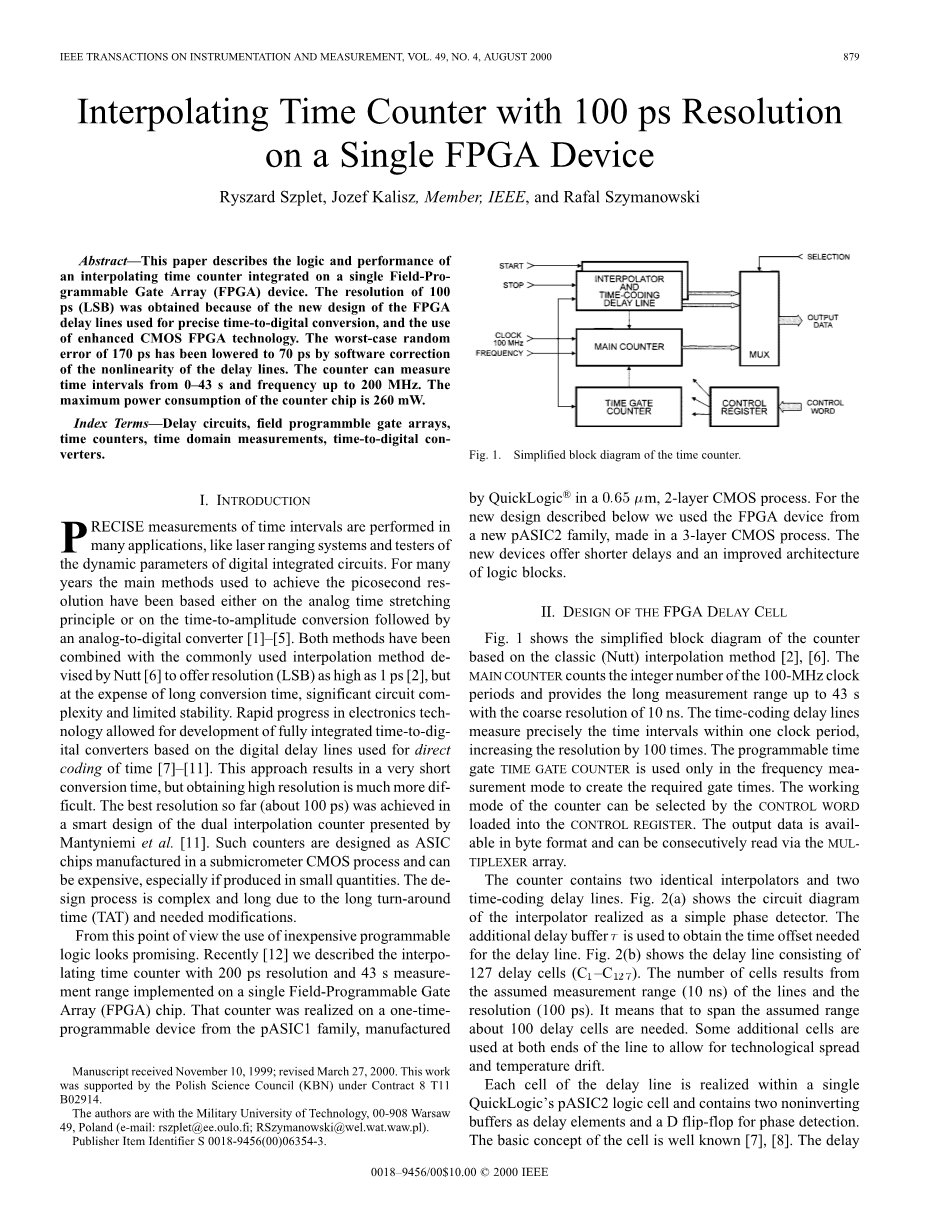

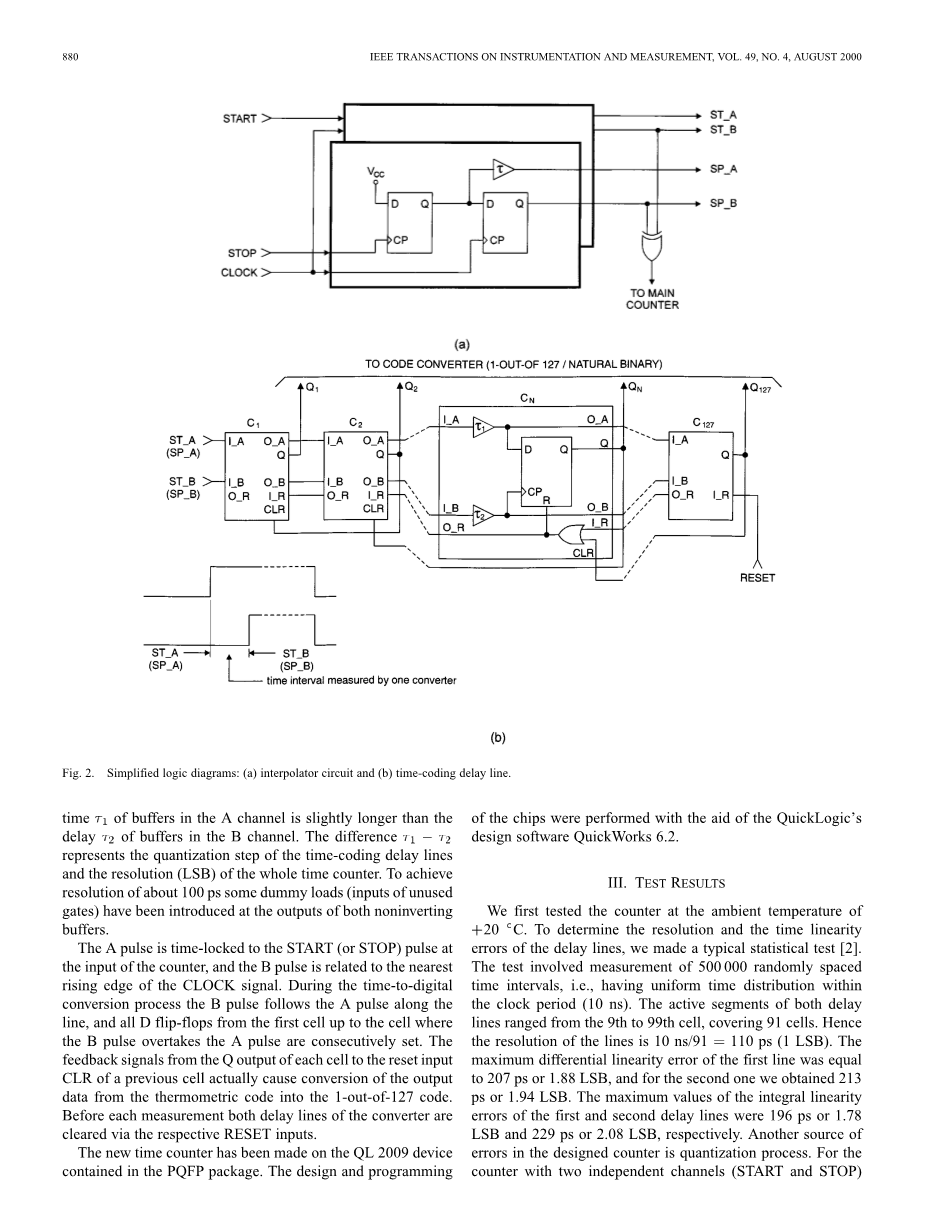

图1显示出了基于经典(Nutt)插值方法的计数器的简化框图[2],[6]。主计数器计数时钟周期100 MHz的整数,提供高达43s的时长测量范围,粗分辨率为10ns。时间编码延迟线精确测量一个时钟周期内的时间间隔,将分辨率提高100倍。可编程时间门计数器仅用于频率测量模式,以创建门所需的时间。计数器的工作模式可由加载到控制寄存器中的控制字选择。输出数据以字节格式提供,并且可以通过多路复用器阵列连续读取。计数器包含两个相同的内插器和两个时间编码延迟线。图2(a)示出了作为简单相位检测器实现的内插器的电路图。附加延迟缓冲器用于获得延迟线所需的时间偏移。图2(b)示出了由127个延迟单元(C–C)组成的延迟线。单元的数量由假定的测线测量范围(10 ns)和分辨率(100 ps)决定。这意味着要跨越假定的范围,大约需要100个延迟单元。在生产线的两端使用一些额外的电池,以允许技术扩散和温度漂移。延迟线的每个单元在一个QuickLogic的pASIC2逻辑单元中实现,包含两个非交换缓冲区作为延迟单元和一个用于相位检测的D触发器。A通道中缓冲区的延迟时间略长于B通道中缓冲区的延迟时间。该差值表示时间编码延迟线的量化步骤和整个时间计数器的分辨率(LSB)。为了达到约100ps的分辨率,在两个非转换缓冲器的输出端引入了一些虚拟负载(未使用的门的输入)。在计数器的输入端,A脉冲被时间锁定在开始(或停止)脉冲上,B脉冲与时钟信号最近的上升沿有关。在时间到数字转换过程中,B脉冲沿着直线跟随A脉冲,并且从第一个单元到B脉冲超过A脉冲的单元的所有D触发器被连续设置。从每个单元的Q输出到先前单元的重置输入时钟的反馈信号实际上导致将输出数据从温度计代码转换为127取1代码。在每次测量之前,转换器的两条延迟线通过各自的复位输入被清除。在PQFP包中包含的QL 2009设备上制作了新的时间计数器。设计与编程其中的芯片是借助QuickLogic的设计软件QuickWorks 6.2完成的。

三、 试验结果

我们首先在20摄氏度的环境温度下测试计数器,为了确定延迟线的分辨率和时间线性误差,我们进行了典型的统计测试[2]。测试包括测量500000个随机间隔的时间间隔,即在时钟周期(10 ns)内具有均匀的时间分布。两条延迟线的活性段均在第9~99个单元格之间,覆盖91个单元格。因此,测线的分辨率为10ns/91110ps(1lsb)。第一行的最大差分线性误差为207ps或1.88lsb,第二行的最大差分线性误差为213ps或1.94lsb。第一和第二延迟线的积分线性误差的最大值分别为196ps或1.78 LSB和229ps或2.08 LSB。设计的计数器的另一个误差来源是量化过程。对于具有两个独立通道的计数器(启动和停止)由量化引起的随机误差的值等于45ps(量化步长),并且远低于由时间编码延迟线的非线性引起的误差。为了降低上述非线性和计数器产生的随机误差,我们在相关软件[12]中对每一行使用各自的积分非线性函数值作为校正向量。这样,两条延迟线的积分线性误差减小到13ps或0.12lsb。收集校准样品所需的时间约为30s。然而,对于给定芯片,该校准过程只能执行一次,并且相关数据可以存储在附带的软件或相关的EEPROM存储器中。为了检查应用校正的效率,我们估计了计数器在一个时钟周期内的一组预定时间间隔的随机误差(RMS值)。正如我们前面所指出的[2],随机误差(模时钟周期)的周期性行为是基于Nutt插值方法的时间计数器的典型特征。为此,我们测量了与时钟异步产生的10个恒定时间间隔,并相差1ns。我们使用了10根不同长度的同轴电缆,每根电缆的延迟量测了5000次。然后,我们的诊断程序通过启用和禁用延迟线的非线性校正计算每个样本的标准差估计值(图3)。校正使随机误差的最大值从170 ps降低到70 ps。校正后,随机误差在整个时钟周期内几乎保持不变。

为了验证计数器在10 ns到10 ms的时间间隔内的准确性,我们使用数字延迟发生器DG535(斯坦福研究系统;1ppm时基误差)作为时间间隔的来源。时间间隔由我们的计数器(100兆赫时钟从发电机HP 8648B获得,时基误差为1 ppm)和商业时间计数器SR620(斯坦福研究系统公司;0.005 ppm时基误差,4 ps分辨率和25 ps随机误差)测量。然后计算每个测量时间间隔样本的平均值。图4示出了两个计数器的平均值的发散。对于最长为1 ms的时间间隔,差异小于73 ps。出现在最长测量延迟(10 ms)处的差异是由所涉及的三个仪器的时基误差(主要是由DG535的时基误差)引起的。

在上述测试中,我们注意到在一个大样本测量(10000)中的一些测量(4-6)的结果与为整个人群计算的平均值显著不同。所观察到的差异达到840ps。这种现象可能是由所涉及的触发器的亚稳态引起的。然而,这种操作的概率低至0.0005。我们还研究了时间计数器在C到C的温度范围内的性能。环境温度影响延迟线中包含的单元的延迟。这意味着每条线的分辨率也会随着温度的变化而变化。我们观察到,这些延迟几乎是线性变化的,并且在两条线中都是类似的。图5示出了由环境温度引起的延迟线的分辨率的变化。分辨率提高了约0.5ps/C,这代表了当时数字转换器的“增益误差”。“偏移误差”由环境温度引起的线的初始部分中未使用的单元数的变化表示。这个数字从20摄氏度时的10变为60摄氏度时的7,或者偏移误差约为4 ps/C。

计数器的温度测试是在整个测量过程中使用为每一行保存的单个校正矢量进行的。利用在20℃下获得的矢量,我们测量了同轴电缆(约39 ns)在0℃到40℃温度下的延迟。图6显示了计数器的随机误差。通过计数器的周期性自动校准,包括校正矢量的识别,可以减小温度效应。

这种校准可以由典型的微控制器使用自适应预测方法定期执行[13]、[14]。图7示出了在每个测试温度下进行校准时获得的随机误差行为的显著改善。当用于计算平均值的样本量很小(小于10)时,单次测量的随机误差很大。当样本量相当大时,会产生一个问题,即温度对计算平均值的影响是什么,因为剩余的误差源(包括延迟线的非线性)随后被有效地平均出来。对于5000的样本量,我们得到了20℃时测得的电缆延迟平均值为39.18ns,在0℃时仅变化了10ps,在40℃时仅变化了30ps。这种微小的变化是由于集成在FPGA芯片中的两条延迟线的对称性。输出数据的计算始终包括从典型的异步校准获得的输入偏移校正[2],在20c下进行一次。

该计数器已在商用FPGA芯片上实现,并在电源电压的标称值(5.0v)下进行了测试。我们还检查了其对允许范围内的电源电压变化的敏感性(即,标称电源电压的5%),但观察到的和测量的时间间隔应保持在统计误差范围内。当电压以8.3ps/V的速率上升时,两个转换器的分辨率都会提高。设计的计数器也可用于频率测量。最大测量频率达到200mhz,相关随机误差为2.4hz。测量以HP 8648B发电机为测量信号源。当时钟关闭时,包含时间计数器的PGachipC消耗25mW,当时钟激活时消耗140mW。最大功率在频率测量期间消散,等于260mw。

四、 结论

采用增强型CMOS-FPGA技术是实现低成本、低功耗、分辨率为100ps(LSB)、测量范围为0~43s的时间计数器的关键,对时间编码延迟线的非线性进行软件校正,使计数器的随机误差降低到70ps(RMS)。计数器还可以测量高达200兆赫的频率。所述计数器可用于许多应用,例如,在具有成本效益和精确的激光测距系统中、在作为专用PC板的虚拟时间/频率计中、以及在自主的移动仪器中。

参考文献

[1] B.Leskovar和B.Turko,“美国宇航局激光测距系统的光学定时接收器,第二部分:高精度时间间隔数字化仪”,劳伦斯伯克利实验室,加州伯克利,报告LBL 61331977。

[2] J.Kalisz,M.Pawlowski,和R.Pelka,“皮秒分辨率的Nutt时间间隔数字化仪的误差分析和设计”,J.Phys。E: 科学。研究所,第20卷,第1330-13411987页。

[3] E.Raisanen Ruotsalainen、T.Rahkonen和J.Kostamovara,“使用时间-电压转换和内置双斜率A/D转换的时间间隔测量”,in Proc。1991年内景。电路和系统(ISCAS91),新加坡,1991年。

[4] J.Kalisz,R.Pelka和A.Poniecki,“激光对卫星测距的精确时间计数器”,修订版。科学。研究所,第65卷,第736-7411994页。

[5] K.Matta和J.Kostamovara,“脉冲飞行时间激光雷达应用的高精度时间数字转换器”,IEEE Trans。仪表。Meas.,第47卷,第521-5361998页。

[6] R.Nutt,“数字时间间隔计”,修订版。科学。研究所,第39卷,第1342-13451968页。

[7] J.F.Genat和F.Rossel,“超高速时间到数字转换器”,法国优先权:1984年5月11日,1988年。

[8] T.Rahkonen和J.Kostamovara,“用于短时间间隔数字化的稳定CMOS延迟线的使用”,IEEE J.固态电路,第28卷,第887-8941993页。

[9] E.Raisanen Ruotsalainen、T.Rahkonen和J.Kostamovara,“低功耗CMOS时间到数字转换器”,IEEE J.固态电路,第30卷,第984

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[238176],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。