英语原文共 27 页,剩余内容已隐藏,支付完成后下载完整资料

AN4325应用笔记

入门STM32F030xx硬件开发

介 绍

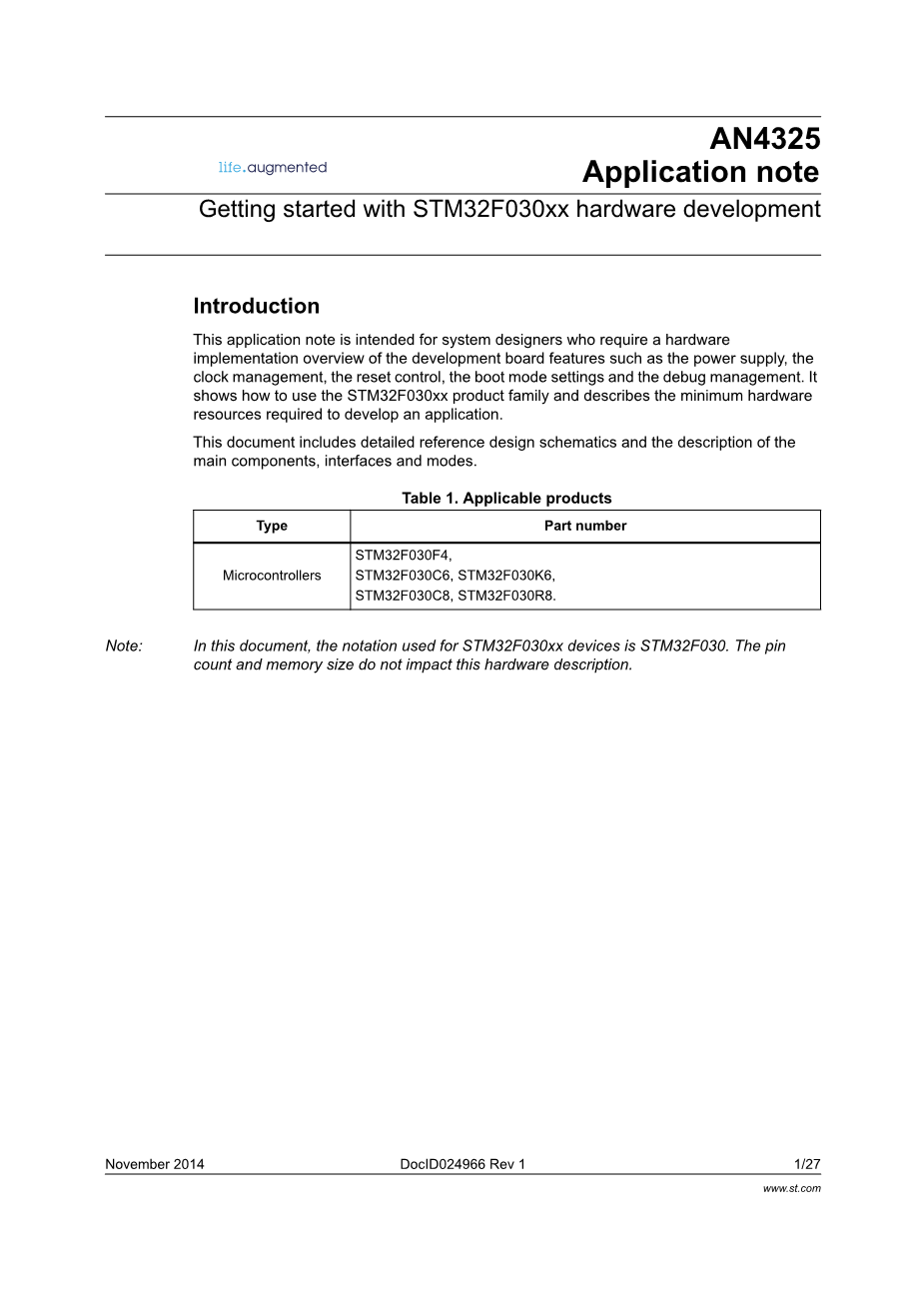

本应用笔记适用于需要开发板功能硬件实现概述的系统开发者,如电源,时钟管理,复位控制,启动模式设置和调试管理系统设计。它展示了如何使用STM32F030xx系列产品,并描述了开发应用程序所需的最低硬件资源。

这个文件包括详细参考设计原理图和主要部件,接口和模式的描述。

表 1 适用产品

|

类型 |

开发板号 |

|

微控制器 |

STM32F030F4, STM32F030C6, STM32F030K6, STM32F030C8, STM32F030R8. |

注意:在这个文件中,用于STM32F030xx开发板是STM32F030。引脚数和内存大小不影响此硬件的说明。

一览表

表 1. 适用产品. 1

表 2. 启动模式 17

表 3. SWD 端口管脚 18

表 4. 必需的组件 23

表 5. 可选组件 23

表 6. STM32F1和STM32F030系列引脚差异 25

表 7. 文档修订历史记录. 26

附图说明

图 1. 供电方案 6

图 2. 肖特基二极管连接 7

图 3. 上电复位/掉电复位波形 9

图 4. 复位电路的简化图 10

图 5. HSE/ LSE时钟源 13

图 6. 主机到板连接 18

图 7. SWD端口连接 19

图 8. 典型布局VDD / VSS对 21

图 9. STM32F030微控制器的参考电路图 24

1 电源和STM32F030系列的复位源 1

1.1 电源方案 1

1.1.1 独立模拟转换器供应 2

1.1.2 稳压器 3

1.2 复位和电源监控器 4

1.2.1 上电复位(POR)/掉电复位(PDR) 4

1.2.2 系统服务 5

2 时钟 7

2.1 高速外部时钟信号(HSE)OSC时钟 7

2.2 LSE 时钟 7

2.3 HSI 时钟 8

2.4 LSI 时钟 8

2.6 时钟的安全系统(CSS) 8

3 启动配置 9

4 调试管理 10

4.1 介绍 10

4.2 SWD端口(串行线调试) 10

4.3 引脚和调试端口引脚 10

4.3.1 串行线调试(SWD)引脚分配 10

4.3.2 SWD 引脚分配 11

4.3.3 内部上拉和SWD管脚下拉 11

4.3.4 SWD端口与标准的SWD接口连接 11

5 建议 12

5.1 印刷电路板 12

5.2 组件位置 12

5.3 接地和电源 (VDD, VDDA) 12

5.4 去耦 12

5.5 其它信号 13

5.6未使用的I / O和功能 13

1 电源和STM32F030系列的复位源

1.1 电源方案

在STM32F030系列具有不同的产品与各电源方案,它包括为了具有用于芯和数字逻辑的内部1.8 V电源的内部稳压器。

有多种供电方案:

VDD从2.4 V至3.6 V :用于I / O和内置1.8V域外接电源,通过VDD引脚外部提供。

VDDA从VDD到3.6 V:为ADC提供外部模拟电源,复位块,HSI,HSI14,LSI和PLL。

VDDA电压电平必须总是大于或等于VDD的电压电平并且必须首先提供。

内核逻辑

(CPU,数位和记忆)

Analog: (RCs,PLL,...)

LSE,RTC

唤醒逻辑

电源开关

VDD

Vcore

NxVDD

调节器

VDD|01

OUT

Nx100nF

1x4.7nF

GPIOs

IN

IO

逻辑辑

NxVss

VDDA

VDDA

10 nF

1nF

VREF

VREF-

ADC

VSSA

MSv32516V2

电平转换器

图 1.1 供电方案

1.1.1 独立模拟转换器供应

为了提高转换精度,并延长供给灵活性,模拟域具有可单独滤波并从PCB上噪声屏蔽独立供电。

ADC电源输入,可在一个单独的VDD引脚。

VSSA引脚提供一个接地连接的隔离电源。

VDDA可以和VDD相等或更高,这使得VDD维持在较低水平,同时还提供用于模拟模块的全部性能。

当使用单电源时,建议VDDA必须在外部连接到VDD,以确保无噪声VDDA使用外部滤波电路。

当VDDA和VDD不同,VDDA必须总是高于或等于VDD。为了保持电/掉电期间VDDA和VDD之间的安全电位差,外部肖特基二极管可以VDD和VDDA之间使用。请参阅数据表允许的最大区别。

VDD

VDDA

VDD

VDDA

肖特基二极管

MS30272V1

图 1.2 肖特基二极管连接

1.1.2 稳压器

复位后稳压器始终处于启用状态。

它在两种不同的模式下工作:

主要(MR)是在正常操作模式(运行)使用,

低功率(LPR)可以在停止模式中使用,其中电力需求减小被使用。

在待机模式下,稳压器处于掉电模式。在这种模式下,调节器的输出是在高阻抗和内核电路断电,诱导零消耗和寄存器和SRAM内容的损失。但是,如果配置了可提供以下功能:

独立的看门狗(IWDG):该IWDG被写入其关键寄存器或硬件选项启动。一旦开始它不能停止除非复位。

实时时钟(RTC):由RTC域控制寄存器(RCC_BDCR)的RTCEN位进行配置。

内部低速振荡器(LSI):由控制/状态寄存器(RCC_CSR)的LSION位进行配置。

外部32.768 kHz振荡器(LSE):由RTC域控制寄存器(RCC_BDCR)的LSEON位进行配置。

1.2 复位和电源监控器

1.2.1 上电复位(POR)/掉电复位(PDR)

该器件集成了一个上电复位(POR)和掉电复位(PDR)电路中始终处于激活状态,并确保在2.4的阈值以上正常运行。

设备保持在复位模式中,当监视的电压低于一个指定的阈值,VPOR/PDR,而不需要外部的复位电路。

POR只监视VDD电源电压。在VDDA必须首先启动且大于或等于VDD。

PDR监视VDD和VDDA电源电压,然而,如果应用程序设计确保VDDA高于或等于VDD的VDDA电源监控可以被禁用(通过编程的专用选项位VDDA_MONITOR),以减少电力消耗。

有关电源的更多细节/掉电复位阈值,请参阅数据表中的电气特性部分。

VDD/VDDA

VPOR

40 mV

滞后

VPDR

与此同时临时修复

复位

063252091

图1.3 上电复位/掉电复位波形

1.2.2 系统服务

系统复位设置所有寄存器进入复位值,除了在时钟控制器CSR寄存器中的复位标志,并在RTC域中的寄存器。当下列事件之一发生时,产生系统复位:

(1)低电平NRST引脚(外部复位)。

(2)系统窗口看门狗事件(WWDG复位)。

(3)独立看门狗事件(IWDG复位)。

(4)软件复位(SW复位)。

(5)低功耗管理复位。

(6)选项字节加载器复位。

(7)电源复位

(8)复位源可以通过检查控制/状态寄存器,RCC_CSR复位标志来识别。

(9)该RESET服务程序向量被固定在内存映射地址0x0000_0004。

提供给设备的系统复位信号是NRST引脚输出。脉冲发生器保证了20mu;s的每个内部复位源的最小复位脉冲持续时间。在外部复位的情况下,而NRST引脚为低电平产生复位。

图 1.4 复位电路的简化图

VDD

RPU

外部复位

)过滤器

系统复位

NRST

WWDG复位

IWDG复位

脉冲发生器 (min 20 us)

电源复位

软件复位

低功耗管理复位

选项字节加载器复位

从待机模式推出

061984192

(1)软件复位

Cortex-M0应用中断SYSRESETREQ位和复位控制寄存器必须设置为强制设备上的软件复位。请参阅Cortexreg;-M0技术参考手册了解更多详情。

(2)低功耗模式安全复位:

为了防止关键应用程序错误地进入低功耗模式,两种低功耗模式下的安全性复位可用。如果在选项位启动,在以下条件下产生的复位:

进入待机模式:这种类型的复位是通过用户选项字节复位nRST_STDBY位启用。在这种情况下,每当执行成功一个待机模式条目顺序,该装置被复位,而不是在进入待机模式。

进入状态:这种类型的复位是通过用户选项字节复位nRST_STOP位启用。在这种情况下,每当成功执行停止模式进入序列,设备重置,而不是在进入停止模式。

(3)选项字节加载器复位:

当OBL推出(13位)在FLASH CR寄存器设置时,会生成选项字节加载器复位。该位由软件启动选项字节加载。

(4)电源复位:

电源复位设置所有寄存器进入复位值,除了RTC域。当下列事件之一发生时,产生电源复位。

电源开/掉电复位(POR/ PDR复位)

退出待机模式

(5)RTC域复位:

一个RTC域复位只影响RTC,LSE和LSI。当下列事件之一发生时产生。

软件复位,由RTC域控制寄存器(RCC_BDCR)设置BDRST位触发。

电源开/掉电复位(POR/ PDR复位)。

2 时钟

不同的时钟源可用于驱动系统时钟(SYSCLK):

HSI 8 MHz的RC振荡器时钟(高速内部时钟信号)

HSE振荡器时钟(高速外部时钟信号)

PLL 时钟

这些器件具有其它辅助时钟源:

驱动独立看门狗和40 kHz的低速内部RC(LSI RC)任选,RTC的用于从停止/待机模式下的自动唤醒。

32.768 kHz的低速外部晶体(LSE晶体)任选驱动RTC

HSI14MHz RC振荡器(HSI14)专用ADC

每个时钟源可以接通或关闭独立地在不使用它,以优化功耗。参阅RM0360参考手册时钟树的说明。

2.1 高速外部时钟信号(HSE)OSC时钟

高速的外部时钟信号可以从两个可能的时钟源产生:

HSE 外部晶振/陶瓷谐振器

HSE 用户外部时钟

谐振器和负载电容器具有,以最小化输出失真和启动稳定时间被放置在尽可能靠近振荡器管脚,负载电容值必须根据所选择的谐振器进行调节。

外部源(HSE旁路):

在这种模式下,必须提供一个外部时钟源。它最多可以有32 MHz的频率。选择此模式由时钟控制寄存器(RCC_CR)设置HSEBYP和HSEON位。外部时钟信号(方,窦或三角形),依赖于频率(参看数据表)〜40-60%的占空比驱动OSC_IN引脚而OSC_OUT引脚可以使用GPIO,参见图5。

2.2 LSE 时钟

LSE 晶体是32.768 kHz的低速外部晶体或陶瓷谐振器。它具有提供低功耗,但高度精确的时钟源用于时钟/日历或其他计时功能的实时时钟外围装置(RTC)的优点。

lt;

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[151429],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。