英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

基于NIOS II处理器的FPGA在单相PFC整流器数字控制中的应用

Deivis Borgonovo, Marcelo L. Heldwein and Samir A. Mussa,

圣卡塔琳娜联邦大学 - UFSC

电气工程系/电力电子学院 - INEP

P.O: Box 5119 – 88040-970 – Florianopolis–SC, BRAZIL

电话: 55(48)3721-9204 /传真: 55(48)3234-5422

电子邮箱:samir@inep.ufsc.br

摘要:FPGA在电力电子转换器的控制中的应用为这种转换器的数字控制带来了新的特点。FPGA器件一直在促进了复杂调制策略的实施。现在,通过在FPGA内部实现数字处理器,就可以以一种简单的方式来执行数字计算。因此,FPGA可以实现一个微控制器的功能,并且在此基础上增加快速组合计算的优点。在这方面,这项工作讨论了在采用NIOS II嵌入式处理器的FPGA中实现电压倍增器升压型PWM整流器的当前自我控制策略的核心问题。对转换器的建模/控制以及两个输出电压控制策略进行了讨论和实验验证。重点介绍了NIOS II处理器应用在功率因数校正中的研究和应用。

索引术语—FPGA,PFC自控,数字控制。

一 引言

FPGA在电力电子转换器的控制中的应用为这种转换器的数字控制带来了新的特点。传统上,FPGA器件一直在促进了复杂调制策略的实施。然而在近期,全面的控制方案已经基于FPGA器件被实现,并且显示了利用FPGA器件实现实际控制加调制的高潜力[1]-[3]。

与CPLD类似,FPGA(现场可编程门阵列)是一种数字硬件可编程组件,这种可编程组件为数字信号处理提供了新的视角,也让数字信号处理发展到电力电子领域。基于其基本块逻辑元件之间的可配置连接,用户可以设计一个具有多个功能的在一个芯片内可并行运行的系统。这个特点和一些其他的特点,让FPGA相比于DSP来说更具有优势,比如硬件优化和数据并行处理的可能性。此外,为一个特定组件制造设计的FPGA可以轻松地装配到具有相似功能的另一个组件中,并且可以在需要时进行修改。FPGA还提供了利用汇编或C语言来实现微处理器的功能。例如,ALTERA提供了一个称为NIOS II的32位处理器。使用这种微处理器,与一个称为SOPC Builder的工具相结合,可以在单个芯片中创建一个或多个系统。尽管FPGA有如此多的优势,但是它们的发展仍然比微控制器/ DSP更复杂,而且成本仍然是一个问题。尽管如此,成本问题正在得到改进。

NIOS II是一款通用的嵌入式处理器系列,具有高性能,专为FPGA而设计,可提供数字处理能力。该处理器系列由三个处理器内核组成,它们实现了一个通用指令集架构,每个处理器内核针对特定的性价比优化,并且都由相同的软件工具支持。NIOS II处理器具有高度的灵活性,其中包括:选择精确的CPU,外设和接口,仅加速所需的功能。它进一步消除了处理器过时的风险。本文的重点是介绍该处理器在单相预调节整流器的数字控制中的应用,并说明了该技术的一些优点和缺点。所使用的控制策略旨在获得单相倍压增压型整流器的功率因数校正(PFC)和直流环节输出电压调节。对转换器的建模和控制以及两个输出电压控制策略进行了讨论和实验比较,其中强调了自控的一些特性。

二 电压双稳态PWM整流器的建模与(自控)控制

单相倍压器双开关升压型PWM整流器如图1所示[4],[5]。它具有以下优点,例如(i)由于电流路径中的功率半导体数量少导致的低导通损耗;(ii)所有半导体都受到输出电压的一半的影响,从而不会增加开关损耗;(iii)关断开关具有相同的接地电位,需要单个绝缘电源,此外可以同时切换。它的主要缺点是输出电容器C1和C2不同时充电,在电源频率处呈现大的纹波。当需要从输出到输入峰值电压的较大比率时,这种转换器非常适合。

转换器可以分为两个转换器,它们分别具有子索引1和子索引2的组件,在图1中它们分别属于转换器Boost 1和Boost 2。 转换器1工作在正电源半周期,如图2所示,其中输出电容器C1通过Db,1的电流脉冲充电,并且能量通过S1和D1传输到电感器L. 互补阶段遵循负半周期,如图2所示。

图1 单相倍压器升压PWM整流拓扑图

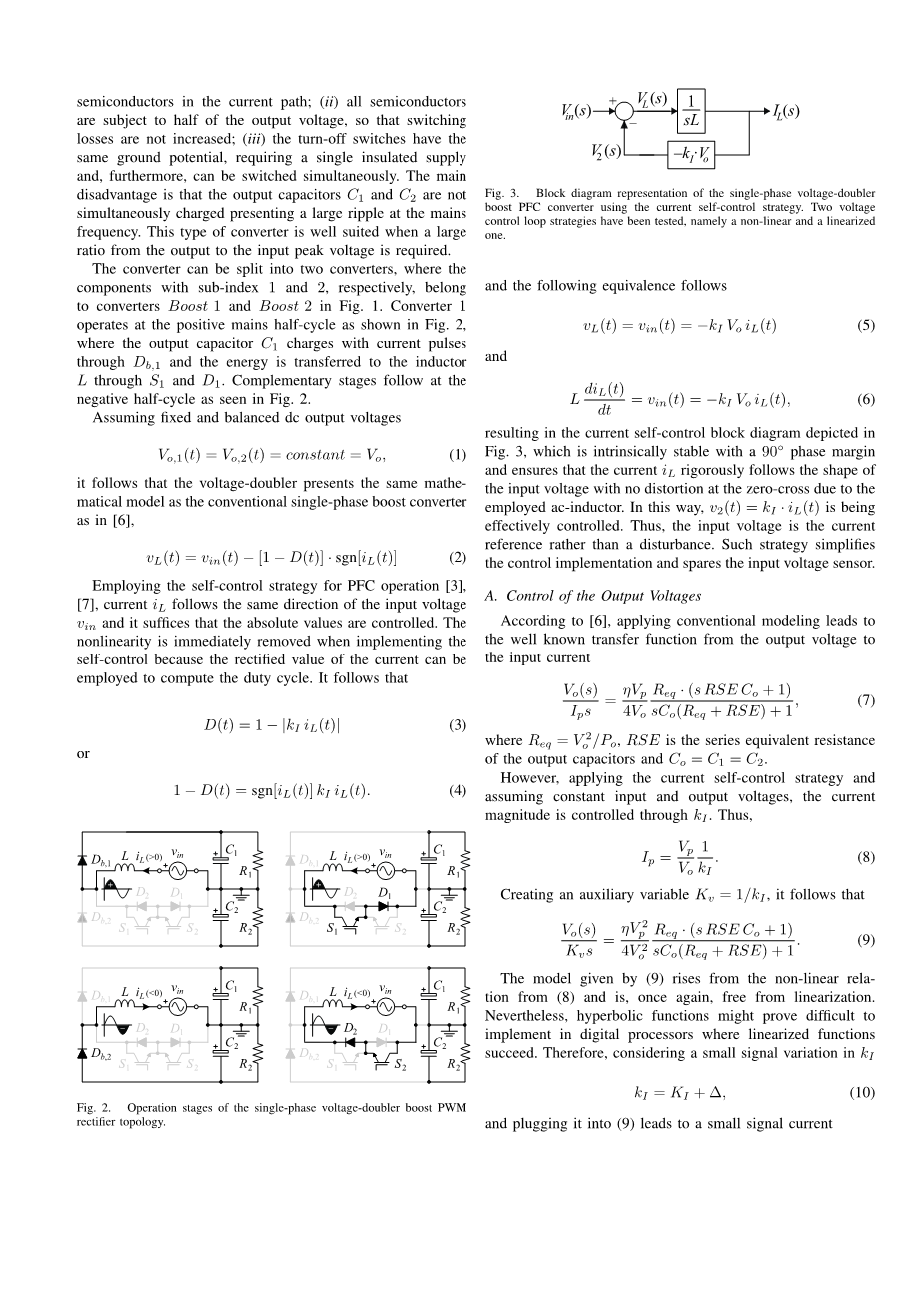

图2 单相倍压增压PWM整流拓扑的运行阶段

假设固定和平衡的直流输出电压:

因此,倍压器具有与常规单相升压转换器相同的数学模型[6],

采用PFC操作的自我控制策略[3],[7],电流iL遵循与输入电压vin相同的方向,并且其绝对值能够得以控制。在实现自我控制时,其非线性立即消除,这是因为电流的整流值可以用来计算占空比。它遵循

或者

并且等效如下

和

上述等效过程导致图3所示的当前自控框图,其本质上具有90°相位裕度的稳定性,并且由于采用了交流电感,所以确保电流iL在零交叉的时候可以没有失真的严格遵循输入电压的形状。这样,v2(t)= kI·iL(t)被有效地控制。因此,输入电压是电流基准而不是扰动。 这种策略简化了控制实现,并且备用了输入电压传感器。

A 输出电压的控制

根据[6],应用常规建模导致从输出电压到输入电流的众所周知的传递函数

其中Req = Vo2 / Po,RSE是输出电容器的串联等效电阻,Co = C1 = C2。

然而,应用当前的自我控制策略并假设恒定的输入和输出电压,电流幅度通过kI进行控制。因此

定义一个辅助变量Kv = 1 / kI,于是,上面的等式就变成

等式(9)给出的模型是由等式(8)的非线性关系上升而来的,并且再次不是线性化的。然而,在线性化功能成功的数字处理器中,双曲线函数可能难以实现。因此,考虑到kI的小信号变化

并将其插入等式(9)中导致一个小信号电流

从等式(12)中得出,

这两种模型,非线性的(9)和线性化的(12)都已经被实现(参见图4)和利用实验测试过了。

图4 使用当前自我控制策略的单相倍压增压PFC转换器的框图表示

B 输出电压平衡和稳定特性

采用传统的当前平均模式控制,并且假设没有电压控制回路,导致恒定的输出功率特性

在自控策略中,方程(15)表明,如果输出电压降低,则输入电流增加。它遵循

因此,通过开环中的当前自控策略,观察到输出电压受负载变化的影响较小。

输入电流是输入电压的图像,其峰值定义如下

假设没有直流分量的输入电压和整个电源周期的单个电压控制回路,kI的值定义为调节输出直流电压。因此,如果不平衡负载连接到C1和C2,则输出电压自然地以稳定的方式搜索它们的平衡。

C 关于现行自我控制的说明

目前采用的自我控制策略以与[8]中提出的技术相似的方式实现了控制。 然而,由于这里的自我控制不是基于占空比,而是基于开关单元上产生的电压,这种方法允许将该控制技术扩展到包括有源滤波器的任何基于升压型转换器。 在更简单的拓扑结构中,占空比和产生电压的概念是直接相关的。 此外,该方法采用线性化模型进行电压控制回路,从而简化了实现。

三 FPGA与开发工具

该系统设计采用ALTERA DE2开发和学习板。该套件提供了EP2C35F672C6 FPGA(33216 个LEs)和一些外设。 主要特点和外设包括:24位音频编解码器(CODEC); 50 MHz和27 MHz晶体振荡器; 76个扩展针脚; 8MB 大小的SDRAM内存,512kB大小的 SRAM内存和4MB大小的闪存。

使用的开发环境是Quartus II Web版本。使用这种开发工具有三种方式,其中两种使用硬件描述语言(HDL),如Verilog和VHDL,第三种使用由ALTERA开发的框图。用户可以同时利用所有这三种环境,以便可以同时利用HDL提供的灵活性和突出功能以及框图的组织性。作为Quartus II Web版本的补充,ALTERA公司还提供了SOPC Builder(系统级可编程芯片)工具。SOPC Builder是一个非常有用的工具,用于创建必须通过总线连接的许多外设的系统。它是专门用于构建具有一个或多个处理器的系统的工具,尽管有些系统不并需要具有处理器。

SOPC Builder工具使用Avalon总线来连接整个系统,Avalon总线是一种智能总线系统,可提供非常高的灵活性和并且符合系统要求。它像看待内存一样去看待外设,为外设分配地址,每个外设都有一个地址,可以在系统编译之前由用户选择。在系统编译时,计算总线宽度,生成最优总线。然后,整个系统被视为一个模块,这个模块的输入和输出都是在编译之前由用户声明。使用SOPC Builder,用户可以利用其自身携带的库中的外设去创建一个完整的系统。ALTERA已经提供了一些这样的外设,如外部存储器控制器,LCD控制器和NIOS II处理器。如果需要,用户可以使用Avalon总线的总线信号创建自己的外设,使其与系统的其余部分兼容。

四 系统硬件和合成块

为了合成项目所需的外设,如PWM调制器和NIOS II处理器系统,它使用了FPGA上可用的硬件实现的基本外设。使用诸如硬件乘法器和内部存储器块的FPGA特性,已经生成了一些专用块来执行基于DSP和微控制器的电力电子和数字控制系统的一些所需功能,如控制器。这些模块与SOPC系统相互连接,SOPC系统可以控制这些模块功能的配置和执行,使其同步以进行正确的操作。

使用SOPC Builder实现的系统工作原理和微控制器一样,同样具有一个处理器,一些外设,并且这些外设可由寄存器和I / O端口配置。该系统由NIOS II / f处理器组成,NIOS II/f

处理器是NIOS II处理器系列中配置最快的一种处理器,使用片上M4k内存模块开发的4kB数据存储器,用于存储在处理器上运行的程序,以及一些并行端口,用于读取输入并传送输出。所有的这些外设均由Avalon总线连接,并且配置为单主机的主从设备,单主机即为NIOS II / f处理器。开发的系统框图如图5所示。

选择好外设和地址正确设置后,就可以将系统编译成实体模块,并导出到Quartus II Web版本中,进行输入和输出的连接,最终完成项目设计。

图5 使用NIOS II处理器的SOPC系统框图

A PWM调制器

调制级基本由计数器和比较器组成。为了获得具有三角载波的PWM,采用了上/下计数器。将该信号与占空比值进行比较,得到比较器输出端所需的PWM波形。

上/下计数器已经使用HDL实现,具有一个时钟输入功能,用来设置PWM频率; 具有复位输入功能,和一个16位输出,用来给出表示三角波形的计数值。所使用的输入时钟频率为60 MHz,所使用的输出频率为48 kHz。输入和输出时钟之间的商为一个PWM周期的计数器转换,也就是1250。将该值除以2,结果值为625,刚好处于三角波形峰值,并且使得占空比的最大值为625。 计数器的输出连接到16位比较器,该比较器将三角形波形与存储在触发器上的占空比值进行比较。当占空比值大于计数器的计数值时,PWM输出为低电平,否则,输出为高电平。图6显示了调制器开发的模块工程框图。

图6 PWM调制器在Quartus II软件中的实现

B ADC控制器

为了对模拟信号进行采样并将其转换为数字表示,设计了一种基于dsPIC30F4011采集板。dsPIC采用96 kHz对变量进行采样,并将数字值通过SPI通信协议发送到FPGA。为了正确接收FPGA中的值,专门设计了一个模块来传送串行数据并在处理器输入端将其转换成并行形式。该模块(参见图7)具有一个定时控制器,用于同步该模块; 移位寄存器,用于将串行数据转换为并行; 一个缓冲区; 解码器,用于识别哪个变量处于缓冲区中; 还有三路采样输出,采样数据为输出电压和输入电流。

图7 A / D转换器控制器框图

五 NIOS II处理器

通常,使用SOPC Builder创建的系统有一个微处理器。NIOS II微处理器是一款高性能32位处理器,可在FPGA中实现,可以在NIOS II IDE中使用汇编语言或C语言进行编程。它的数据总线和程序总线是分开的,通常也被称为哈佛架构,并具有简化指令集计算机(RISC)架构。它可以通过三种不同的方式进行配置:NIOS II / e(600-700 LEs),处理器的经济版本,运行缓慢,没有部分指令,如乘法; NIOS II / s(1200-1400 LEs),允许乘法指令并以中等速度运行的标准配置; NIOS II / f(1400 - 1800 LEs),最快的配置包括整套指令,但最大的配置也占据相当的空间。

NIOS II处理器的算术和逻辑运算在通

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[139459],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。