英语原文共 11 页,支付完成后下载完整资料

LTE应用的CMOS包络跟踪的功率放大器

摘要:用0.18微米CMOS工艺制作了一个CMOS包络跟踪(ET)功率放大器。这个模块中包括了电源调节器、功率放大器、和被PCB板上印刷的输出变压器。CMOS功率放大器利用在输入端进行二次和三次谐波控制和输出端对二次谐波短路以提高功率放大器的线性。对影响级联差分结构线性的因素进行了研究和优化,提出了在PCB上添加一个输出变压电路的方法,可以减小损耗增加功率放大器的效率。提出了不使用数字预失真技术(DPD)实现功率放大器高线性和高功率的共栅共源晶体管的栅极ET方法。对于工作在1.85GHz,带宽为10MHz和使用正交调制峰均比为7.5dB的LTE信号来说,在平均输出功率在26dBm的情况下,ET CMOS功率放大器模型可以实现达到34%的功率附加效率,2.8%的误差向量幅度和34.2dBc的相邻信道功率渗漏比(ACLR)。相对于单独使用功率放大器的电路,使用ET的功率放大器电路使LTE信号的总电路消耗减少了10%,降低到34%。

索引:CMOS,有效率的,包络跟踪(ET),线性,手机,LTE

Ⅰ引言

个人电脑和移动电话的功能已经被集成在智能手机中。高速的无线传输要求对大量的数据进行快速的处理。为了应对功率损耗的增高,人们要求电路要有更高的效率和容量更大的电池。智能手机的损耗和尺寸是这种消费产品很重要的特性。人们正在通过努力提高智能手机效率、速度、损耗、尺寸等每一个部件的设计以克服这些问题。在这些部件中,功率放大器是提升效率和降低智能手机损耗和尺寸的瓶颈。

移动手机的LTE基础设施标准正在被建立并且由于大量对数据高传输速率的需求,手机已经开始支持LTE通信。但是高数据传输速率导致了巨大的信号带宽和高的峰均比(PAPRs)。通常来讲,高的PAPR信号在一个比较低的平均输出功率水平下会降低功率放大器的效率,因为给功率放大器提供的电源是固定的而输出负载仅仅在瞬时功率达到顶峰时被优化。

现在已经有一些技术可以提高功率放大器的效率以提高高PAPR信号的放大。Doherty技术使用四分之一波长转换器调节负载阻抗以调节回退功率和峰值功率。根据功率水平,这项利用了可重构输出网络的技术也可以增加高PAPR应用的效率。但是这些技术对于RF的带宽很敏感,需要复杂的输出匹配网络但是会产生损耗。在【4】中介绍的开关电容器技术可以通过控制电源开关通断把负载调节效应最大化,但是因为快速通断的MOSFET的击穿电压很低,该技术很难产生高的功率以适应有源器件。异相功率放大器也可以在回退功率中实现高的效率,但是它有一个动态的功率范围限制还需要一个复杂的复合电压网络。包络消除和恢复(EER)与包络跟踪(ET)通过调节功率放大器的供应电压提高效率。传统的EER结构因为幅度和相位路径的延迟失配导致其工作的非线性,并且在低的输出功率情况下,它们还会遭遇严重的巨大输入功率泄露问题。ET技术对于延迟失配的敏感度更低,并且可以不使用额外的线性化技术而通过使用一个线性的功率放大器和源供应调节器实现其线性工作。因此,鉴于ET技术的多模/多波段性能本篇论文应用了ET技术。

在移动手机设备中,一个RF集成电路(RFIC)和基带集成电路(IC)芯片被集成在单片上以减少它的尺寸和损耗。但是功率放大器通常是基于砷化镓(GaAs)工艺制造的,因为GaAs较高的可靠性和工作性能。功率放大器甚至将会与RFIC一起被集成到CMOS工艺中或者与开关电路一起被集成到SOI工艺中,由此以降低设备的损耗和尺寸。

硅基底的缺点在于它的击穿电压比较低,没有接地的后通孔,比较高的饱和电压(拐点电压),更大的损耗与和元素周期表中的第三与第五族相比具有更严重的非线性。即使SOI工艺通过在氧化物覆盖层之下使用高电阻的基底减轻了基底上的损耗,在CMOS工艺中仍然有别的电路级上的问题需要关注。一种共源共栅结构减轻了低崩溃电压的问题。输出变压器的使用帮助解决了没有后通孔和较高的饱和电压的问题。一个在源上的虚拟接地点提供了有效的地端并且使RF的增益增加。电压结合导致了晶体管的输出阻抗的增加。CMOS功率放大器主要的非线性是由输入电容参数引起的,可以通过二次谐波控制或者电容补偿技术改善。虽然二次谐波短路在输出端被广泛利用以提高CMOS功率放大器的线性和效率,但是输出端的二次谐波控制对于线性的重要性已经被忽视了。

在本篇论文中,我们分析了非线性的产生过程中,共栅晶体管在共栅共源结构中的贡献并且说明了二次谐波控制在输入和输出端的重要性。本文也研究在输入端对三次谐波控制的影响。为了设计出相比于HBT(异质结双极晶体管)功率放大器更具优势的CMOS功率放大器,我们提出了在功率放大器中设计一个低耗的变压器。并且ET技术被用来克服CMOS功率放大器固有的低效率。本论文的组织顺序如下所示。第二部分说明了一个CMOS功率放大器利用谐波控制电路提高线性和设计一个输出变压器把损耗降到最低。第三部分描述了一个混合开关供应调节器的布局设置和强调了ET运行中的问题。第四部分显示了运行和测试的结果。

Ⅱ CMOS功率放大器的设计

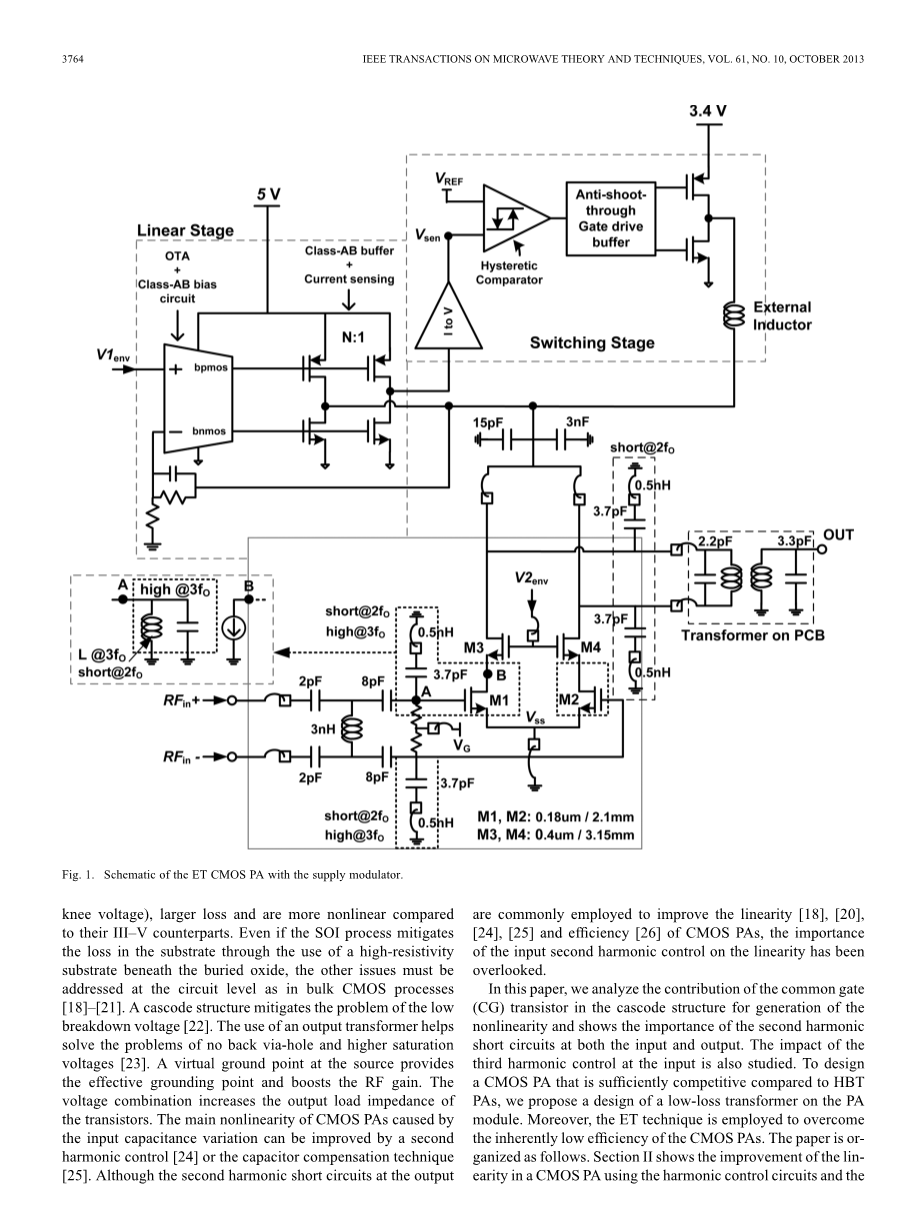

图1是一个使用了CMOS功率放大器的ET发射机和一个混合的电源调节器的示意图。这个功率放大器使用了一个单阶差分结构去将电源退化降到最低。0.18微米薄的氧化物和0.4微米厚的氧化物晶体管堆积在一起产生了一个保护电路崩溃的共栅共源结构。另外,谐波控制电路还被用在放大器的输入和输出端。

A. 谐波控制电路用来提高功率放大器的线性

以前的文献注重CMOS功率放大器中共源(CS)晶体管的非线性研究,作者在【28】中描述了AM-PM失真主要是由于CG部分中的Cgd的非线性造成的。在这部分,我们更加深入地分析了在共栅共源结构中CG晶体管对于谐波产生的贡献。

晶体管栅极和源极之间的电容随着通过接线端子的电压增加而增加。晶体管栅极和漏极之间的电容也随之增加而且由于电压在漏极被放大所以这个参数更加重要,但是相比与栅极的电压漏极的电压极性会发生反转。因此,在较高输入电压水平下的电容是比较大的,在较低的输入电压水平下电容较小。这些非线性的电容使正弦输入电压波形发生失真。在输入端的二次谐波控制电路补偿了由于晶体管输入电容的非线性导致的输入失真信号,运行结果更加线性化。

输出端的二次谐波短路电路除去了二次谐波电压,从而降低了导致三阶交调失真(IMD3)和五阶交调失真(IMD5)成分的上边频,并且提高了设备的效率。在结合输出端差分结构仅仅去除偶次谐波成分,但是并不能降低IMD3和IMD5,因为交调失真(IMDs)可以由在漏极受到限制的二次和三次谐波产生。一个三次谐波短路电路通过降低五次谐波产生成分三次谐波分量,也能提高功率放大器的线性。但是它的贡献相比于二次谐波控制电路是很小的,因为三次谐波分量远低于二次谐波分量。

为了证明二次和三次谐波控制电路的作用我们做了一次仿真。电压和电流的波形图与他们的谐波分量显示在图2中。两个CMOS功率放大器在输入端加和不加二次谐波控制电路拥有相同的理想输出变压器以证明控制电路的作用。两个功率放大器在输出端都有二次谐波控制电路并且稳定系数K超过1.5当输入信号从0上升到10GHz。共栅共源结构漏极的电压设置为3.5V,CS和CG晶体管的栅极电压分别设置为0.48V和2.3V。在用连续波(CW)仿真时测得的波形的输出功率是26dBm。在这个设计中一个3.7pF的电容和0.5nH的电容被用来与二次谐波在3.7GHz产生共振。差分结构的输入阻抗与50Omega;相匹配,单独的共栅共源结构的负载阻抗设置为12.5欧姆。

在晶体管的等效模型电路中,功率放大器的谐波是由于固有的非线性电容和非线性的依赖电流源导致的。晶体管的三极区也会产生导致非线性。共栅共源结构通常比一个单独的CS结构有更高的非线性,因为两个晶体管堆积在一起具有更多的非线性源。

图2和图3显示了CG晶体管对于功率放大器线性的影响。在输入端没有二次谐波控制电路的功率放大器的输入电压波形会有很高的失真并且有一个大的导通角在dc电平线上,这是由输入电容引起的二次谐波成分导致的。输入电压的二次谐波分量被放大然后转变成输出电流和CS晶体管的漏极电压。正如图2(b)和(c)描述的那样,如果在输出端没有二次谐波控制电路的话,那么在CS晶体管漏极的电压和电流的二次谐波分量是比较大的。二次谐波分量混合着基频和由于CG晶体管gm的非线性产生的三次谐波分量 ,因此导致了IM3和IM5的产生。并且CG晶体管使用了一个厚的氧化物栅极,相比于使用薄的氧化物作为栅极的CS晶体管,CG晶体管有一个比较高的饱和电压。较高的饱和电压修割了电压波形然后产生了比较大的非线性。因此,正如在图3中显示的那样,没有二次谐波短路电路的功率放大器相比于带有该电路的功率放大器会产生更多的IMD成分。

在输入端的二次谐波短路电路在为三次谐波提供一个开路中起了很大的作用,因为一系列的电容和电感,可以在三次谐波中等效成为一个可以和CS晶体管2.9pF的平均输入电容相共振的0.27nH的电感。因此,在图片2(a)中显示的巨大的三次谐波分量低于基频的电压,但是在CS晶体管的漏极超出了基频电压,所以把CS晶体管的漏极电压平方并增加基频电压的幅度,如图2(c)所示。如图2(e)和(f)所示,CS晶体管较高的基频漏极电压导致CG晶体管较低的电压浮动,拐点电压变高,从而保证线性运行。相比于加有控制电路的情况,没有二次谐波短路电路的电压浮动会更严重地破坏CG晶体管的三极区域和截止区域。

图3(b)显示了CS晶体管和CG晶体管对于共栅共源结构产生非线性的贡献。带和不带二次谐波控制电路的CS晶体管漏极的IMD3曲线绘制在图中。选取在IMDs上下之间的最差IMD曲线进行分析。在信号通过CG晶体管之前,两种情况下CS晶体管部分的IMD3水平在-35dBc以下并且有显著的最佳点。但是当信号通过CG晶体管之后,IMD3特性恶化。当CS晶体管的电压和电流的二次谐波分量比较高的时候,IMD3会降低更多。当三次谐波电压被用一个额外的电容设置成几乎为零时同时保持相同的基频和二次谐波电压,高的三次谐波输入电压对于IMD3的影响也被显示在图中,结果在中高功率范围比IMD3高5dB/1dB。总的来说,在共源共栅结构的输入端,二次谐波控制电路有效地通过减少CS晶体管和CG晶体管之间的二次谐波分量提高了线性,三次谐波控制通过保证在线性区域内的电压浮动也帮助提高了线性。

讨论高于和低于IMD3s的不平衡性是很有意义的。这种不平衡性通常是由记忆效应引起的,这种记忆效应是指之前由二阶失真引起的f1-f2/f2-f1和2f1/2f2的分量和f1/f2分量混合在一起然后与有着不同相位的2f2-f1/2f1-f2三阶相互作用叠加在一起,导致了IMD3上下不同的幅度值。被人所熟知的降低记忆效应的方法是在漏极或者接收结针对f2-f1使用一个耦合电容。虽然没有接地的后通孔,然而CMOS工艺提供了在晶体管源的终端接入额外的记忆效应的源,这个源通过焊线与地相连。在图3(c)中,由二阶失真引起的f1-f2/f2-f1和2f1/2f2分量被源终端所限制,导致IMD3在输出部分的非平衡性。f1-f2/f2-f1分量比2f1/2f2分量大35dB,它可以通过在栅极和漏极终端的二次谐波短路电路而被降低。IMD3上下的相位在仿真中被测量结果为1度和-30度,显示出不同的相位向量求和导致了IMD3的非平衡性。源终端理想的接地会调整IMD分量,降低在输出端IMD3的非平衡性。在实际的操作中,倒装芯片工艺可以降低主要导致记忆效应的f1-f2/f2-f1分量。图3(d)显示了在有和没有二次谐波短路电路中,主要通过在差分CS晶体管结构源终端加入理想的地降低IMD3的非平衡性。在这次仿真中,在没有源电感的情况下,调整栅极偏置电压优化放大器,直到静止电流从41mA上升到56mA。

对于提高一个单端的共栅共源结构的线性想法可以应用于差分结构。对于CMOS功率放大器来说,差分结构被用来最大程度减少源的退化。理想情况下,漏极电压的偶次谐波分量是一个复合模式会被输出变压器所排斥,但是如果没有一个合适的偶次谐波终端,谐波会被限制然后与基频相互作用产生三次谐波失真。通常来说,变压器并不是总是在相位上相差180,而是有一些相位失配。图4中所画显示,在输入和输出端的二次谐波短路电路使功率放大器对输出变压器的相位失配不是那么敏感。在二次谐波控制电路的作用下,IMD3的特性和线性输出功率几乎是相同的,它们的相位差保持在10度以内,这对于变压器来说是完全可以实现的。

B.输出变压器的设计

基底的参数如损耗电导率和介电层的厚度都会影响输出变压器的线性质量因子Q和两条线之间有效的耦合系数。一旦选定了确定的基底,金属线的宽度和长度决定了自感和变压器的Q。有效的耦合系数k是由两条金属线之间的间隔所决定的。图5(a)描述了普通四层评估板的层信息,它被用来做功率放大器的组件。对于功率放大器模块来说,这种基底相比于以层压板为基础的复合层基底有较高的损耗因数(0.025),较厚的介质层(42.5微米),比较高的最小间隔(100微米)。图5(b)展示了输出变压器的3D模型。金属线

资料编号:[3224]

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。