英语原文共 4 页,剩余内容已隐藏,支付完成后下载完整资料

一种适用于功率放大器的过压保护电路

齐默尔曼(Niklas Zimmermann, Ralf Wunderlich) 斯蒂芬·海恩(Stefan Heinen)

德国亚琛工业大学集成模拟电路D-52056研究室

电子邮箱:zimmermann@ias.rwth-aachen.de

摘要——随着移动通信设备的发展,对于更高的集成度以及更加低廉的花费的需求也随之日益增加,使用CMOS功率放大器,而不是使用GaAs功率放大器或者SiGe功率放大器的趋势也随之越来越大。尽管对于CMOS而言,它的价格相对便宜,但是也存在着射频性能不够好以及击穿电压过低等缺点。这种问题尤其体现在功率放大器(PA)的输出级上面,即当负荷与输出不匹配时,会导致高电压驻波比(VSWR)现象的产生,并且在功率放大器(PA)端会输出高峰峰值电压。本篇文章中提出了一种在0.13微米CMOS工艺下设计的27dBm功率放大器(PA)的驻波比(VSWR)保护电路。以及相应的控制回路,该回路机理为:通过检测在PA输出端的高电压振幅尖峰值来进行动态调节以降低功率放大器(PA)的增益,从而进一步降低输出电压的摆幅以达到理想值。

- 引言

功率放大器是每个射频发射机的最重要部分之一。大多数的功率放大器是基于SiGe或GaAs工艺制造而成的,而接发传输器以及基带电路则更加偏向于使用更低水平的CMOS工艺技术制造。COMS构成的PA芯片(终端功放芯片)可以实现将整个完整的大型无线电系统集成在单个芯片里面,从而很可观的减少花费成本以及覆盖面积。现代深度亚微米CMOS工艺的性能正在朝着更加接近与SiGe以及GaAs PA的方向发展并且该趋势十分具有吸引力,但是COMS管PA的设计对于设计者来说仍然是是一个艰巨的挑战。其中一个很关键的问题就是,在所有可能会发生的情况之下保证基本要求的可靠实现。尤其是一个对于标准CMOS晶体管的低击穿电压而言十分关键的问题,即在负载失配时PA输出端的变化将会导致VSWR的升高进一步导致其毁坏。

本论文提出了一种用于CMOS功率放大器的VSWR保护电路。该电路也可以被设计用来作为一个附加的输出功率为27dBm的两级差分功率放大器。该PA的设计目的是为了集成在DECT电话芯片中,与参考文献[1]类似,其详细设计细节和测试结果请见参考文献[2]。

本文结构如下:首先,介绍了PA的非理想影响,在第三部分中提供了可能的解决方案,在第四部分中给出了PA的整体结果和设计,紧接着对VSWR保护电路做了详细的介绍,最后提供了具体的测试及仿真结果。

- PA的非理想因素

CMOS PA面临的的可靠性问题主要包括以下三个方面:

- 会导致模拟CMOS电路的RF性能退化的热载流子效应[3]。即当漏极电场强度过高时,沟道电子将对Si-SiO2表层产生破坏,因而会出现热载流子效应。这种效应会导致MOSFET的开启电压增大,进而导致跨导降低。

- 由于电场作用下导电粒子运动造成元件或电路失效的现象——电迁移。这种现象或许会导致线路之间产生空隙甚至差距乃致芯片损坏。尤其是当较大的直流电流密度存在同一个线路中时,极易引发电迁移这个问题。

- 最后,CMOS晶体管中一个十分致命的威胁,就是栅氧化层或PN结暴露在过高电压下时会被直接击穿。根据其种类的不同,0.13m工艺的CMOS晶体管的栅极击穿电压分布于4.5~4.8V之间,PN结反向击穿电压约为7V.

- 天线负载失配而引起的过高电压

发生在天线上的负载失配会导致传输信号的反射,从而形成驻波。反射波的幅度以及相位可以通过反射因子p来度量。如果传输信号幅度为Vf,那么驻波的最大幅度即为Vmax=Vf(1 |rho;|)。因此当负载失配严重时,驻波幅度将会飙升至传输信号幅度的两倍。负载失配的衡量尺度以及表示方法为VSWR——驻波电压最大值与最小值之比,即驻波比。

(1)

A.驻波比(VSWR)保护机制

高电压驻波将会加速由于电迁移与热载流子效应而在PA上引发的永久性退化,甚至会导致晶体管立即被击穿。一种解决CMOS晶体管击穿问题的方式,就是从它的工艺水平入手,并且在标准呢CMOS晶体管工艺制造这个步骤中引入与高电压兼容的集成晶体管(比如:厚栅氧化物晶体管或漏极扩展MOS(样品)[4])。在这些改进中需要额外增加步骤与工艺手段,因此也增大了额外的开销。同样,这些射频晶体管的RF性能表现也要低于一般的标准晶体管。最后,大量的半导体公司属于“无制造半导体”,并且在独立的半导体生产厂制作,使得这类特殊的高电压兼容晶体管的集成变得更加艰难。

因此,解决线路水平上的问题是一个具有希望的替代方法。即设置电压反馈电路,用此种方法来避免过电压。然而,该电路只适用于双极型晶体管,并不适合于CMOS PA功率放大器。

本项目提供了一个用于CMOS功率放大的保护电路。它会感应在PA的开路漏极输出处的临界高电压,并动态降低放大级的偏置和增益。其概念原理除了实现方面略有差别外,基本类似于[6]。在下一节中将讨论两个主要组成部分——过电压检测器和偏置调节器。

- PA拓扑结构与设计

图一 带有过电压保护电路的功率放大器框图

该图片器件名称从左至右从上到下依次为:

级间匹配偏置 第一级放大器 级间匹配偏置 第二级放大器 不平衡变压器

偏置控制 偏置控制 电压探测器

上图所呈现的带有驻波比(VSWR)保护机制的功率放大器包括一个两阶段AB类功率放大器作为核心以及输出电压控制回路。该系统拓扑结构框图如上图所示。控制回路负责感应第二级输出端口电压的变化。如果输出摆幅超过一定临界值下的驻波条件或超过电源供应电压最高限制,便会发生偏置并因此使得该阶段的放大增益降低,并重新建立起无目的性的输出波动摆幅。

全差分功率放大器(PA)需要单端转换。除芯片之外的所有CMOS均采用13微米工艺制造而成。

- 功率放大器的设计核心

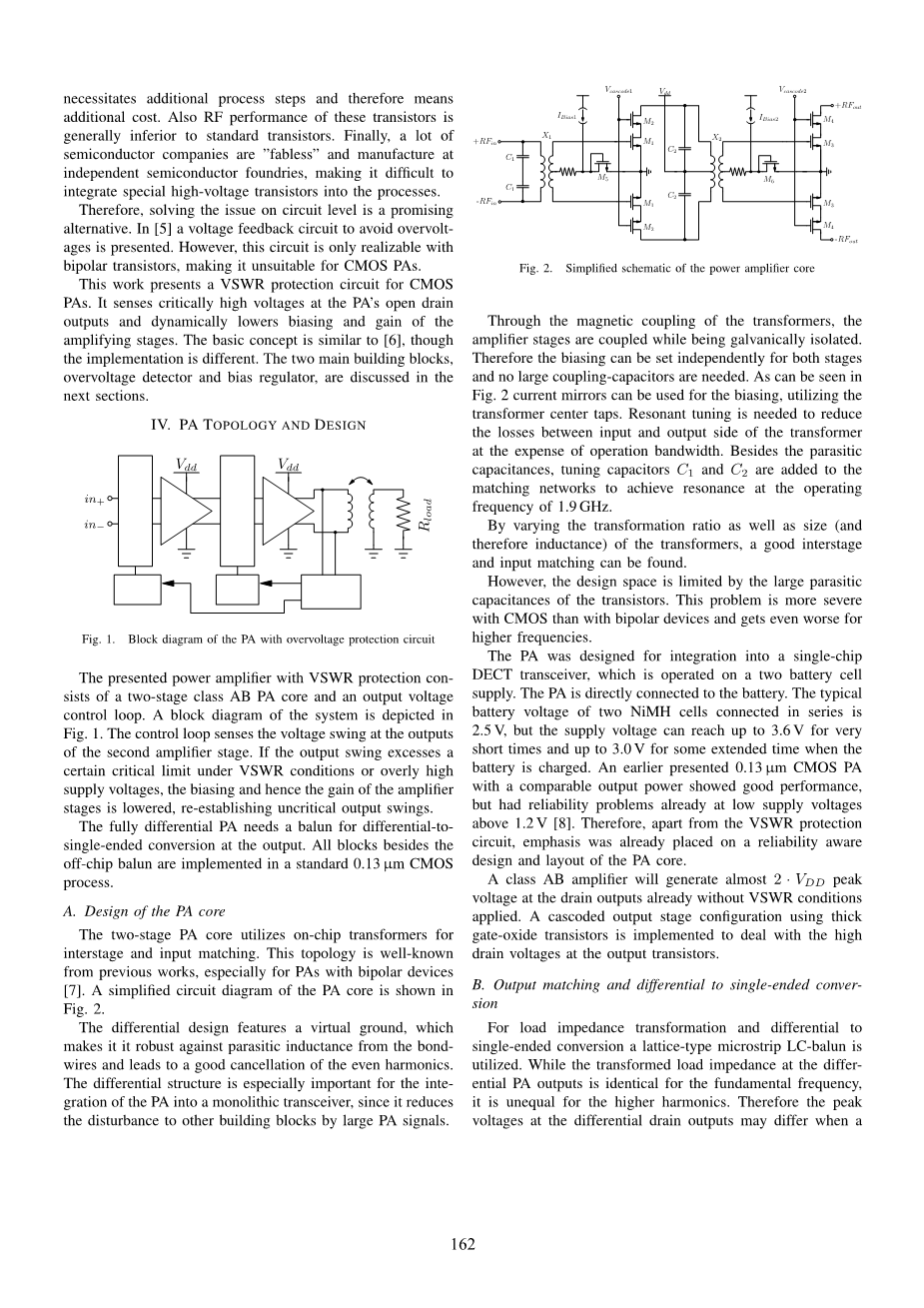

该两级功率放大器核心是采用功率放大器极间和输入的匹配。其拓扑结构就目前研究现状而言是众所周知的,尤其是对于双极型器件功率放大器,图二提供了一种简化的功率放大器(PA)的核心结构电路图。

该差分设计采用了虚拟平面技术,这使得它在线路方面可以抵抗寄生电感,从而使得偶次谐波被很好地消除。差分结构对于功率放大器与单片收发器的集成有着十分重要的作用,因为它可以减少大功率放大器对其他组成部分造成的的干扰信号。

图二 简化的放大器主要原件纲要图

通过对变压器进行磁耦合,放大器的两个分级被进行有序的联系与隔离。所以偏置可以被设置为独立的两个阶段,并且不需要大型的耦合电容器。从图中可以看出,利用变压器的中心抽头,两个镜像电流可以用于实现偏置。谐振需要进行适当调整以减少输入和输出变压器在操作带宽转换损失与费用。此外,除寄生电容,还引入了调谐电容C1与C2并将其添加到匹配的网络以实现1.9GHz的频率共振。

通过变换转化率与变压器尺寸(乃至电感)的大小,一个性能优良的极间匹配和输入匹配就得到了实现。

然而,该设计中,通过电容晶体管的空间是有限的。并且这个问题在CMOS管上所体现的要比在双极型器件上体现的更为严重,而且甚至在获取更高频率这方面做得更差。

功率放大器(PA)被设计专门用来集成到一种单芯片的DECT(Digital Enhanced Cordless Telecommunications ,数字增强无绳通信) 系统上,该系统在两个电池电源的供应下工作,功率放大器与电池直接相连。其中两个串联的镍氢电池的电压是2.5V,但是在电池进行充电时,电源电压在很短的时间内就可以达到3.6V,并且在接下来持续的时间内可以达到3.0V.

有一种曾被较早提出过的0.13micro;m CMOS 功率放大器也具有相似的输出功率,并且也曾表现出良好的性能,但在低电源电压高于1.2v[8]时器件的可靠性也成为了一种问题。因此,除了需要发展VSWR保护电路之外,有关于功率放大器PA核心的可靠性感知设计和布局方面的问题也已经引起了重视。

在没有驻波比保护电路应用的情况下,一个经典的AB放大器会在输出电压峰峰值达到接近2VDD时就早已经被耗尽了。而一个使用厚栅氧化物晶体管的共源共栅输出级控制匹配系统可以用来在输出端实现解决高耗尽电压的问题。

- 输出匹配以及单端的差分变换

格状微波传输带LC不平衡变压器被用来进行负载阻抗转换以及差分单端变换。差分功率放大器输出的变换负载阻抗,虽然对于基频是相同的,但对于高次谐波却是不相等的。因此,当施加VSWR电路的时,差分漏极输出的峰值电压可能不同。因此,两个漏极输出的峰值电压必须通过过电压检测器来监测。

- 过电压检测

过电压检测电路如图三所示。

图三 过电压检测示意图

如图所示,该电路由n个二极管链和一个并联电阻电容组成。在二极管链末端的节点RF输出端与功率放大器PA的漏极输出节点相连。在正常情况下,二极管的N·Vknee膝电压是要大于最大漏极电压摆幅的。因此输出电压没有被负载,功率放大器PA的性能也不会发生退化。如果实在在VSWR情况下,功率放大器的峰值输出电压会超过N·Vknee数值,并且会有产生超过二极管链和电容器充电电容的电流的趋势。电压控制被用来控制偏置,其按照控制电压等于RF输出电压减去膝电压的规律增长。一旦VSWR条件失效或者不再被应用,就需要高阻抗并联电阻器为电容器放电,是的功率放大器回到正常的工作状态。另外,也可以用低偏置电阻替换高阻抗电阻,这样可以隐形中节省芯片的面积。

显然,这种情况下,是不可能使用二极管连接的PMOS晶体管来代替真正的PN二极管的。因为Cbuffer进行充电时,与二极管连接的晶体管的漏极电压会变得很大,从而将会导致耗尽型二极管产生反向偏置电压,从而使得大电流进入散结,该现象会产生造成晶体管损坏的风险。

- 动态偏置调节

控制电压Vcontrol被用来调节放大级的偏压点。为了实现该功能,图4所示的电路应用了图2电路曾使用的简单镜像电流反射电路的扩展电路。如图4所示,M3和感应器分别代表变压器的输出级和次级(第二级电路)侧。在正常的操作系统中,控制电压Vcontrol为零,而射频电压Vref是一个比它高得多的参考电压。因此,在左侧分支中,PMOS晶体管M2l的输入阻抗要比右侧分支的晶体管M2r的输入阻抗高。因此,当前所有偏置电流只能够通过右侧分支。Ir是放大器放大阶段的参考电流,而晶体管M1r和M3构成了当前的镜像电路,这与图2中所示相同。如果检测到临界射频电压RFout过高,控制电压Vcontrol就会像前面解释的那样上涨。这会造成晶体管M2r的输入阻抗增加,从而使得偏置电流分布在两个平行的分支上。使得反映到“有源”晶体管镜像电流减小,放大阶段和增益的偏置便会随之降低,从而使得输出电压波动降低,并使其恢复到非临界值。控制环路的速度受到输出级中晶体管M3的大栅极电容的限制。当控制电压Vcontrol突然上升时,需要花费几个射频(RF)信号周期,直到直流电压偏置Vbias达到一个稳定的新值。如果出现极大的失配并由此产生在射频输出(RFout)节点处的电压波动,那么输出级晶体管立刻被击穿的风险仍然存在。该问题可以通过增加额外的晶体管M4来解决,即如果控制电压Vcontrol显示出可能会导致M3击穿的电压,该附加晶体管M4便会导通。在这种情况下,M4会使M3的门立即截止,从而使功率放大器PA在一个射频周期内完成转换。其中,M4开关的控制电压可以用电阻分压器调节。该变化可由以下公式表示:

仿真结果表明,此种偏置调节不仅应当应用于输出阶段,而且要同时应用于两个功率放大阶段。驱动阶段的输出电压可以有几个伏特的摆动,可以使输出阶段变成“自偏压”,即使它的偏置被减少为零。同时可以减少驱动级的偏置,从而实现在没有“自偏置”效应的情况下节省控制环路的操作。

- 测量及模拟结果

- 功率放大(PA)核心

在1.9 GHz的工作频率下,制造出的功率放大器(PA)核心部分峰值输出功率为27.4 dBm(即550mW),且PAE为34%。在CW条件(continuous wave condition 连续波条件)下进行测量,5dBm的输入功率为2.5V。其小信号增益为24dB。结论:该功率放大器(PA)符合DECT(Digital Enhanced Cordless Telecommunications 数字增强无绳通信)的要求。

- 过电压保护电路

图5展示了功放输出级处的级联以及有源器件的漏极-源电压的模拟结果。图5(a)显示了额定操作条件(2.5伏电源和50个天线负载)下的漏源极电压。图5(b)显示,在过大负载失配的情况下,电源电压将会提高到3.2 v。正常情况下PA的排泄输出节点的最大电压为5V,但是在最坏的情况下可以上升到大约6V。此时如果没有控制回路的调节,高的漏极电压将会导致功放输出级的故障。在正常运行情况下,该保护电路不会降低功放的性能。

全文共5955字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[14828],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。