英语原文共 11 页,剩余内容已隐藏,支付完成后下载完整资料

Microprocessors and Microsystems 28(2004)115-125

www.elsevier.com/locate/micpro

FPGA的VHDL-Forth核心

Richard E. Haskell*,Darrin M. Hanna

奥克兰大学计算机科学与工程系,美国密歇根州罗彻斯特市48309

2003年6月16日收到; 2004年1月29日修订; 于2004年1月29日接受

摘要

Forth编程语言通常在某个特定的微处理器上运行。 多个Forth引擎被设计为直接执行Forth指令,通常在单个时钟周期内执行。 随着高密度FPGA的出现,在FPGA中实现高性能Forth内核已经可行。 本文描述了使用VHDL的Forth内核的设计,该内核已在Xilinx Spartan II FPGA上实现。 举例说明了编译为VHDL代码的高级Forth程序,该程序实现了嵌入FPGA中的ROM。 在FPGA中使用Forth内核可以实现数字系统的快速原型设计。 实验表明,在相同的时钟速度下,相同的Forth程序在FPGA Forth内核上执行速度比在68HC12单片机上快近30倍。 这个相同的程序在FPGA Forth内核上的执行速度比在相同的68HC12上运行的同等编译的C程序快6倍。 Forth内核可在www.tigs.com/fc16上的EDIF文件中找到,它可以包含在VHDL项目中,并使用大约30%的Spartan II FPGA。

关键词:第四核心; VHDL; FPGA; 基于堆栈的微处理器; 快速原型

- 介绍

Forth已经在许多微处理器上实现,包括Motorola 68HC12 [8]。 由于FPGA的密度(以等效门的数量而言)已经增加而其成本已经降低,因此考虑将包括微处理器内核在内的所有功能放入同一个FPGA中形成真正的系统芯片。 在微处理器内核上运行的软件也将以指令的形式存储在相同的FPGA中。 Forth是一种使用数据堆栈和后缀表示法的编程语言。 Chuck Moore在20世纪60年代后期发明了Forth,并用汇编语言编写了小型机。 他的想法是创建一个简单的系统,允许他使用汇编语言写出比他所能写的更多有用的程序。 Forth的本质就是简单 - 总是尽量以最简单的方式做事。 Forth是一种以模块化思考问题的方式。 它是极端模块化的。 Forth中的所有内容都是一个命令,每个命令都是一个有用的模块。 有一个与Forth命令相关的操作,即命令自我执行。 四个指令先接受参数

在数据堆栈上执行,然后将答案返回到数据堆栈中。

Forth已经以多种不同的方式实施。 Chuck Moore原来的Forth拥有所谓的间接线程内部解释器。 其他Forths使用了所谓的直接线程内部解释器。 每当你从一个Forth命令到下一个命令时,这些内部解释器就会一直被执行。 最近在一本关于嵌入式系统的书中描述了Forth的一个独特版本,称为WHYP(发音为whip) [8]。 WHYP代替命令行来帮助你编程。 WHYP就是所谓的子程序线程化的Forth。 这意味着内置在68HC12中的子程序调用机制用于从一个WHYP字转到另一个WHYP字。 换句话说,WHYP文字是68HC12子程序。

因为Forth(和WHYP)程序组成

命令序列,最常执行的指令是对下一个命令的调用; 即以传统的Forth执行内部解释器(NEXT),或者在WHYP中调用子例程。 典型Forth程序执行时间的25%以上用于调用下一个命令 [16]。 为了克服这个问题,Chuck Moore在20世纪80年代设计了一种名为NOVIX的计算机芯片,它可以在单个时钟周期内调用下一个字(相当于子程序调用) [5]。 许多Forth原始指令

也可以在一个时钟周期内执行。 NOVIX芯片的设计最终被出售给哈里斯半导体公司,并重新设计为RTX 2000 [6]。 还开发了类似的32位Forth引擎 [12,13,15]。 在20世纪80年代,Chuck Moore设计了一款名为ShBoom的32位微处理器,该微处理器拥有64个8位指令,并被用于和DRAM的连接 [17]。 后来,Chuck Moore和CH Ting设计了Ting所描述的MuP21 [18,19]。 在1999年我们设计了W8X微控制器 [7] 这是基于这些早期Forth发动机开发的想法。 它是使用VHDL设计的 [1] 并已在奥克兰大学的初级课程中由学生在赛灵思FPGA中实现 [9]。 W8X和W8Z的一种变体,只实现特定程序中使用的指令,也已在FPGA中实现 [10].

本文介绍了在Xilinx Spartan II FPGA上实现的完整16位Forth内核的设计。 第2节描述了F16 Forth内核的整体架构。 数据堆栈和数据堆栈指令在第3节中描述。功能单元实现算术,逻辑,移位和关系

指令详见第4节。返回堆栈的操作和返回堆栈指令在第5节中讨论。控制单元的操作在第6节中描述。使用此Forth内核进行快速原型开发的一些示例 [11] 在第7节中给出了Xilinx Spartan II FPGA的实验结果。实验结果表明,在第8节中给出了与Eratosthenes Sieve相同的Forth程序在FPGA Forth内核上执行的速度比在相同时钟速度下的68HC12微控制器快25倍。FC16 Forth核心的操作在第9节中总结。

- FC16 Forth核心

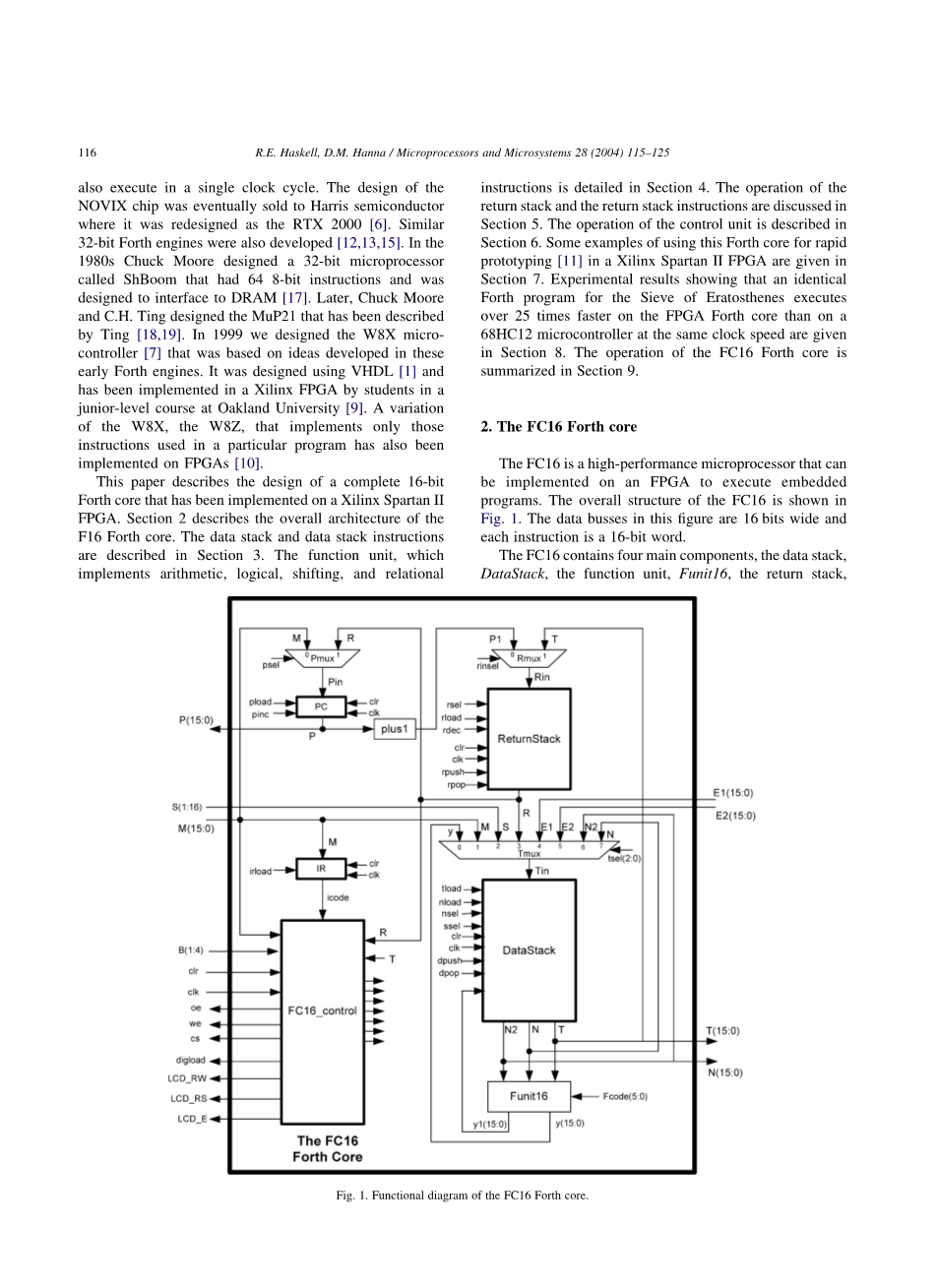

FC16是一款高性能微处理器,可以在FPGA上执行以执行嵌入式程序。 FC16的整体结构如图所示 图。1。 该图中的数据总线宽度为16位,每条指令为16位字。

FC16包含四个主要组件,数据堆栈,

DataStack,函数单元,Funit16,返回栈,

图2.使用FC16 Forth内核的顶层设计示例。

ReturnStack和控制器FC16_control。 FC16还包含一个程序计数器(PC),其输出P包含下一条指令的地址,是FC16内核以外显示的程序ROM的输入。 图2。 ROM的输出是信号M,它可以加载到指令寄存器(IR)中,通过多路复用器Tmux压入数据堆栈,或通过多路复用器Pmux加载到PC中。

使用FC16内核的示例如图所示 图2 代表了顶级VHDL设计,该设计被下载到由Digilent,Inc.生产的Digilab D2开发板上的Xilinx Spartan IIE FPGA上。 [2]. 图2 显示将Digilab D2开发板连接到由Digilent,Inc.开发的DIO2外设板所需的信号 [2]。 Digilab DIO2主板包含16个LED,一个16 2液晶显示器,8个开关,15个按钮,4个七段显示器,一个VGA端口和一个PS / 2端口。 参考文献中给出了一个使用FC16内核在DIO2外设板上制作计算器的例子。 [11].

pound;

其他内存和I / O模块可以添加到顶层设计中 图2。 例如,RAM模块将从N总线(数据堆栈中的第二个元素)输入数据,并从T总线(数据堆栈的顶层元素)输入地址。 RAM的输出将通过E2总线反馈到数据堆栈顶部。 我们将使用写使能(我们)信号将数据写入RAM模块。 包含常量数据的ROM模块将其地址输入连接到T总线,并将其输出连接到E2总线。 将描述访问这些RAM和ROM模块的特别的四个命令。

数据堆栈顶部可以通过8位1多路复用器Tmux从8个不同的信号中加载,如图1所示 图。1。 其中一个信号是S,可以连接到外部开关。 指令S @会将S的值压入数据堆栈。 第3节提供了数据堆栈操作的更详细描述。

- 数据堆栈

FC16数据堆栈是一个修改后的堆栈。 表格1 显示FC16执行的基本堆栈操作。 这个数据栈的体系结构如图所示 图3. 图4 显示了使用由堆栈控制器控制的32 16 LogiCore双端口RAM实现的32 16堆栈。 堆栈控制器将堆栈实现为传统堆栈,其中包含完整和空标志的推送和弹出指令。 当push为#39;1#39;且pop为#39;0#39;时,堆栈将d(15:0)处的值推送至写入地址wr_addr,该地址表示存储器中下一个空位置。 wr_addr和读地址rd_addr同时递减。 操作完成后,输出q(15:0)包含堆栈顶部的值。 当pop为#39;1#39;且push为#39;0#39;时,读取和写入地址都会增加。 与传统堆栈不同,当pop和push都为#39;1#39;时,顶层元素将被替换为d(15:0),而不会推动堆栈。

pound;

pound; pound;

FC16数据堆栈如图所示 图3 由两个组成

16位寄存器用于数据堆栈的顶部和第二个元素,后面跟着修改后的32 16堆栈 图4。 这些寄存器Treg和Nreg用作#39;假顶#39;

pound;

表格1

FC16数据堆栈操作

操作码名称 功能

0000 NOP 没有操作

0001 DUP 重复T并推送数据堆栈。

Nlt;=T; N2lt;=N

0002 SWAP 交换T和N:Tlt;=N; Nlt;=T

0003 DROP 放下T和弹出数据堆栈。 Tlt;=N; Nlt;=N2

0004 OVER 将N复制到T中并推入数据堆栈。

Tlt;=N; Nlt;=T; N2lt;=N

0005 ROT 顺时针旋转堆叠顶部3个元素。

Tlt;=N2; Nlt;=T; N2lt;=N

0006 -ROT 旋转堆栈顶部的3个元素

逆时针。 Tlt;=N; Nlt;=N2; N2lt;=T

0007 NIP 拖放N和数据堆栈的其余部分。

T不变。 Nlt;=N2

0008 TUCK 将T复制到N并推入数据堆栈的其余部分。 N2lt;=T

0009 ROT_DROP 丢弃N2并弹出数据堆栈的其余部分。

T和N不变。 相当于ROT DROP

000A ROT_DROP_SWAP 删除N2并弹出数据堆栈的其余部分。

T和N交换。

图3.数据堆栈

和数据堆栈中的“假秒”元素。 该体系结构对于支持涉及前三个堆栈元素的指令的单时钟周期执行是必需的。

顶部寄存器Treg的输入可以来自使用8中所示的8对1多路复用器的8个可能来源之一 图。1。 寄存器堆栈中的第二个元素Nreg的输入可以来自Treg,来自函数单元的输出之一y1,或者来自修改堆栈的顶部,堆栈32X16。数据堆栈指令至多运行于

数据堆栈的前三个元素。 上面描述的对栈32的修改对于支持涉及第三栈元素的操作是必需的。 例如,指令ROT将Treg中的值移动到Nreg,即Nreg中的值到堆栈32的顶部16(数据堆栈中的第三个元素)和堆栈顶部的值32 16到Treg

全文共13268字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[12607],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。