英语原文共 9 页,剩余内容已隐藏,支付完成后下载完整资料

采用读写分离和BIST可编程定时控制电路的低活性和泄漏功耗的SRAM

摘要

高速低活性和泄漏功耗的SRAM存储器是为移动处理器开发的。这个用于低泄漏电流的电池阵列和电源切断的外围电路的睡眠模式处于待机模式,在主动模式下,通过使用虚拟地面控制的分布式解码器,泄漏功率降低了约4%。此外,采用读写时序控制减少了约25%的写入电流。带有嵌入式内置自测试(BIST)的可编程定时控制与紧凑时序控制的实现,使由于工艺变化的延迟变化得以减缓,从而产生较低的活动能量。设计的16 kbit的存储器是由65 nm LP工艺制造。它的运行速度为1.24千兆赫,同时消耗的泄漏功率为1.16兆瓦,在待机模式下,11.1 PJ /访问活动能量的一个词的长度为32位。

关键词:SRAM BIST 存储单元 地址解码器 传感放大器

- 说明

处理器在在成为移动设备的一个重要组成部分,其消耗功率直接影响电池寿命。因此,根据需要的工作频率减少功耗是必要的。处理器在处理多媒体或游戏时,必须以高速运行,而高速运行的周期通常是短的,而处理器则是在低速或待机模式下运行的为一个较长的时间。在移动处理器,片上SRAM通常嵌入来获得高性能,而SRAM消耗比重较大的处理器电源[1,2]。 此外,由于越来越高的多媒体分辨率和大规模的游戏需求,更高的性能是必需的。

因此,低漏电流和有功电能的SRAM在所需的工作频率是一个在移动处理器的最重要的组成部分。

大多数发表的低功耗SRAM设计有有限的操作频率,使他们不适合高速移动处理器[ 2–4 ]。本次设计的主要重点是低功耗和相对高的速度及小面积的漏电功耗。嵌入式存储器设计目标的移动处理器,在1兆赫的频率工作。此内存设计规范和性能的总结,由表1给出。在1.2 V,它可以运行在高达1.24 GHz,活性能量和待机漏电功率分别为11.1 PJ /访问和1.16。

这项工作采用了几项设计技术,高速和低功耗内存在65 nm LP技术。使用标准阈值晶体管和一个分布式解码器的位单元用于高性能。低功耗是由细胞阵列和外围电路断电由睡眠控制实现[2,5]。读写分和嵌入式BIST的可编程定时控制降低活化能。

本文组织如下。内存全局结构,分布式解码器和低泄漏技术在第2节中描述。第3节提供有关位单元选择的信息。读写分和变化承受时序控制电路在第4节中描述。第五节包括测量结果和在65 nm CMOS技术的记忆状态比较。

- SRAM 组织结构

2.1. 整体结构

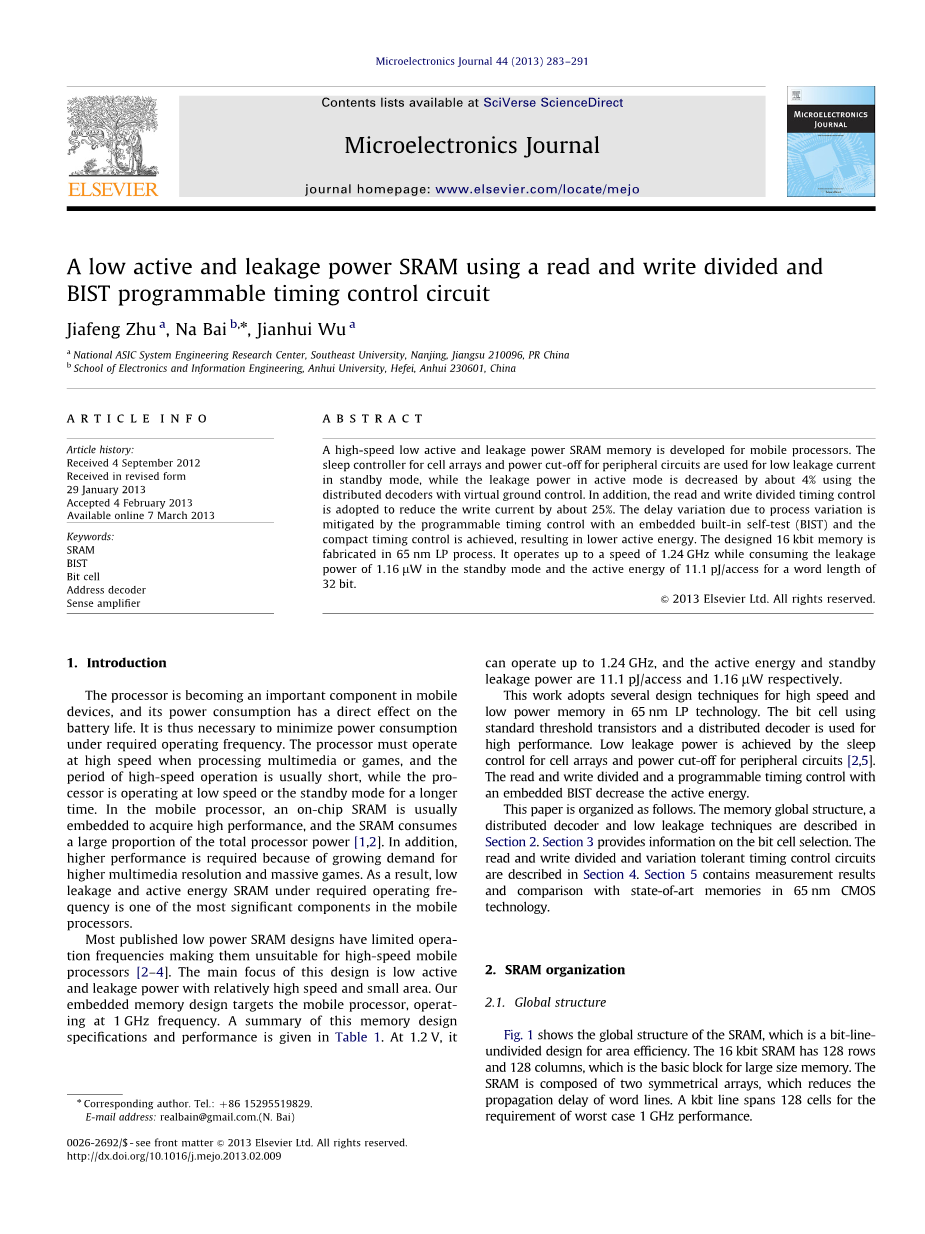

图1显示了SRAM的整体结构,这是一个面积效率位线分割设计。16 K位的SRAM有128行和128列,这是大容量存储器的基本块。SRAM是由两个对称的阵列,从而减少字线的传播延迟。一个千位线跨越了128个单元来满足最坏情况下的1GHZ的性能需求。

表1 SRAM概要

图1 SRAM的全局结构

2.2 分布式解码器

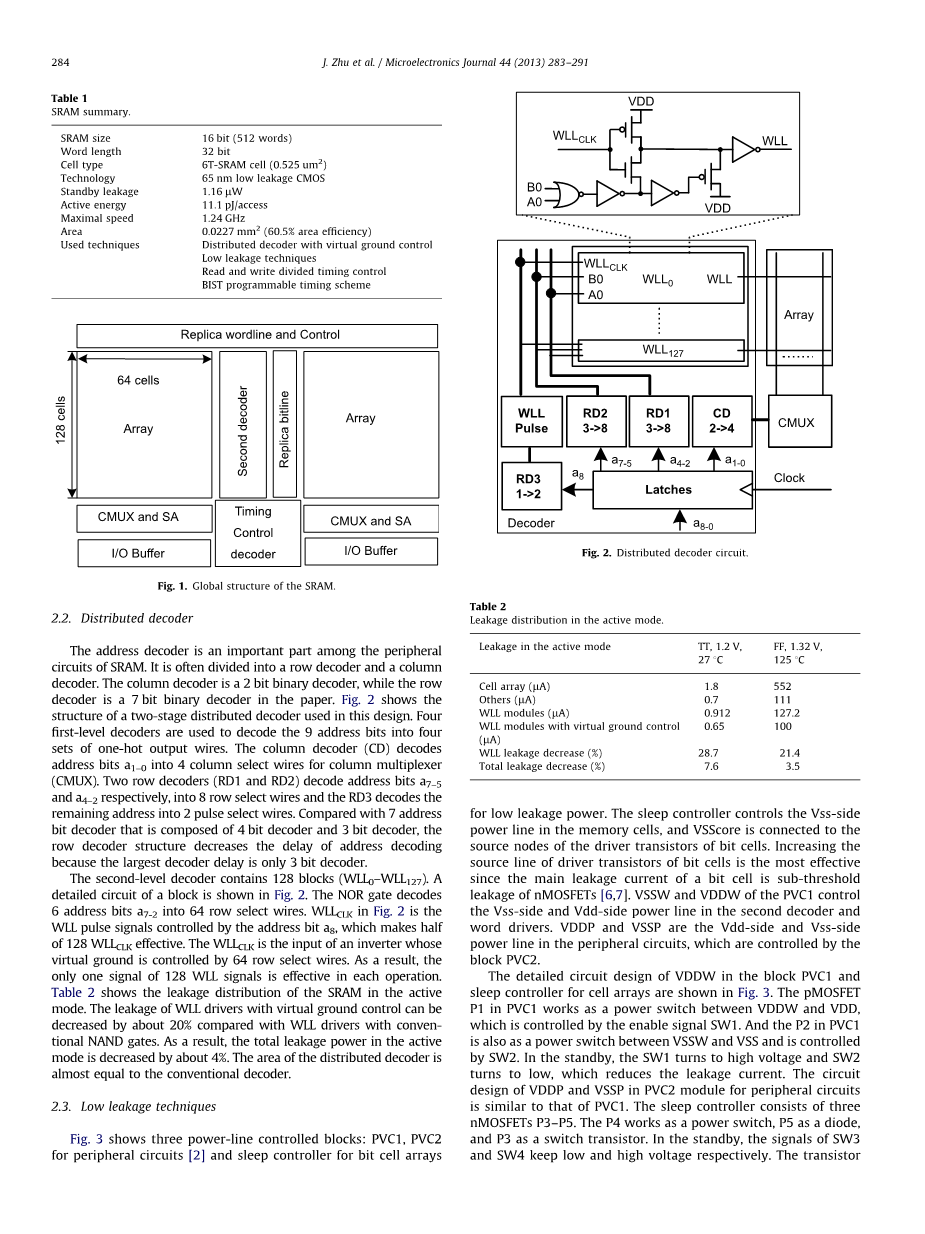

地址解码器是SRAM电路外设中的重要组成部分。它通常被分成一个行解码器和一个列解码器。该列解码器是一个2位二进制解码器,而行解码器是一个7位二进制解码器。图2显示了在本设计中使用的两级分布式解码器的结构。四个第一级解码器被用来解码9个地址位的一个热输出线的四个开关。列译码器(CD)解码地址位A1–0在4列选择线(CMUX)中为列多路复用器。两个行解码器(RD1和RD2)译码地址位分别为A7–5和A4–2,成8行选择线和RD3剩余地址为2脉冲选择线。与4位译码器和3位译码器组成的7位地址位译码器相比,该行解码器结构减少了地址译码的延迟,因为最大的解码器延迟只有3节解码器。

第二级解码器包含128块(WLL0–WLL127)。如图2所示,是一个块的详细电路图。与非门解码6位地址a7-2成64行选择线。图2的WLLCLK是将由地址位A控制DE脉冲信号,这使得一半的128WLLCLK有效。WLLCLK是虚拟地面由64行选择线控制的输入反相器。因此,在128个WLL信号中只有一个信号在操作区域是有效的。表2显示了SRAM在主动模式下的泄漏分布。虚拟地面控制的WLL驱动泄漏与传统NAND门的驱动相比下降约20%。其结果是,在有源模式的总漏电功耗降低了约4%。分布的解码器的面积几乎等于传统的解码器。

图2 分布式译码电路

表2 主动模式下的泄漏分布

2.3 低侧漏技术

图三显示了3个电源线控制块:PVC1,外围电路的PVC2和低泄漏功率单元阵列的睡眠控制器。睡眠控制控制着存储单元中的VSS侧电源线,和连接到比特单元驱动器晶体管源节点的VSS核心。增加比特单元驱动器晶体管源级线是最有效的方法,因为位单元的主要泄漏器件是nMOSFET的亚阈值泄漏。在PCV1中的VSSW和VDDW控制着在第二解码器和字驱动器中的VSS侧线和VDD侧电源线。VDDP和VSSP在外围电路的VDD和VSS侧电源线,是由PCV2模块控制。

在模块PVC1和睡眠细胞阵列控制器VDDW具体电路设计如图3所示。在PVC1中,pMOSFET P1作为VDDW和VDD之间的电源开关,它是由使能信号SW1控制。在PVC1中的P2也是作为作为VSSW和VSS之间的电源开关,它是由SW2控制。在待机状态下,SW1变成高电压,SW2电压变低,从而降低了泄漏电流。在PCV2中的VDDP和VSSP的外围电路模块电路的设计是和PVC1类似的。睡眠控制器是由P3-P5三个nMOSFETs组成。P4作为电源开关,P5为二极管,和P3为开关晶体管。在待机状态时,信号SW3和SW4分别保持低电压和高电压。P5包含晶体管单元驱动器晶体管,如图3所示。复制驱动晶体管的数量影响定时激活检测放大器。

图3 低泄漏电源控制方案

图4显示了6T单元主要的亚阈值漏电流在最角落的VSS核心电压的功能(FF,1.32 V,125 1C)。如图4所示,如果6T单元左边是低电压,在待机模式下,一个单元的泄漏主要是由一个NMOS驱动ND2,NMOS传递NG1,PMOS负载PL1。当VSS核心提高到0.3 V,在记忆单元的器件泄漏电流减少了81%,总泄漏量降低62.3%。由于VSS核心电压的增加,泄漏电流进一步减小,但记忆单元变得不稳定。根据计算,在待机状态当vss核心增加到0.3 V和1.08 V电源,平均持有静态噪声容限(mhsnm)除以偏差持有静态噪声边缘(shsnm)约为12。而VSS核心是0.6 V,mhsnm / shsnm仅为6.4。根据第3节的描述,mhsnm / shsnm也必须满足大于6的产量要求。此外,当VSS核心是高于0.3 V时,泄漏电流逐渐减小。因此,在待机状态下,vsscore设置为约0.3 V。

图4 一个6T位单元的亚阈值泄漏

泄漏电流通过睡眠晶体管与晶体管的大小成比例。如图3所示,位单元的驱动 nMOSFETs作为偏置控制。美国的目标是选择偏置 nMOSFET P5的数量。在待机模式下,一个单元的总泄漏电流约为驱动NMOSFET当 vss核心约0.3 V时的三倍,因此可以通过以下的亚阈值电流模型通用方程[8]: (1)

当亚阈值因子满足和,8 kbit单元阵列的睡眠晶体管数量是K.在稳定状态下,8 Kbit的单元泄漏电流应等于睡眠晶体管的亚阈值电流。使用如下公式可以计算K值:

(2)

通过公式(2),K值可以简单的通过VSScore的电压计算出来。越高的VSScore要求K值越小。在本设计中,VDD和VSScore分别为1.2V和0.3V。因此,K值被设置为16。然而,nMOSFET体效应是不包括公式(2),睡眠晶体管K的计算数字是保守估计的。

- 位单元选择

为了限制位单元区域,单元中的晶体管被选为最小尺寸。最常用的是传统的具有一个缓冲区读取的6T和8T SRAM单元。为了小面积,只要稳定性足够,6T位单元是首选的。从图5分析,6T单元稳定性满足要求。

与6T单元相比,在区域大时,8T单元可以在低电压区操作。为了进行比较,两个单元用最小的晶体管来实现。8T单元下拉晶体管的尺寸是因为不需要读噪声容限而降低。如表3所示,在最差的情况下,由于8T单元更小尺寸的下拉晶体管,8T单元泄漏电流是比6T低22%。然而,8T单元的面积是比6T单元大35.5%。此外,为了更高性能8T SRAM应适应分位线。因此,该区域的8T SRAM花费将更大。作为结果,选择6T单元和在SMIC 65 nm技术下的0.525毫米的单元面积。 此外,传统的CMOS工艺,具有标准的阈值电压(Vth)之间的选择和高电压MOSFET。作为比较,为了更详尽的的单元选择,要分析比特单元的三个最重要的属性。

在设计上,两个标准Vth和高Vth细胞都选择的最小面积0.525平方毫米。图5显示了一个单元作为供给电压的函数的三个性质。位电池漏电流在每单元微微安培输出,微安培读电流。给出的平均静态噪声容限(msnm)在读操作中通过标准偏差(SSNM)单元的稳定性划分。当msnm / SSNM大约为6时,相应的故障率是10-9时正态分布假设,这对应于99.99%的芯片产量为16 kbit SRAM [9]。在本文,最低运行电压的SRAM是0.8 V。因此,99.99%以上的芯片产量可以满足应用的要求。模拟还表明,在最差区域里写能力的2位单元是足够的。

图5 两个SRAM位单元的三个主要特性作为一种基于标准阈值MOSFET和高阈值MOSFET的模拟电源电压变化的函数

表3 两个6T单元和8T单元的比较

如图5所示,高Vth单元的泄漏电流是比标准的Vth单元下降约67%。然而,较高的阈值电压对存取晶体管的电流存在负效应,使SRAM的性能降低。此外,由于比较高阈值电压的MOSFET的更多变化,一位单元的稳定性下降时,电源电压较低,而高Vth点单元稳定性低于标准Vth单元。标准电压的性能比较(SVT)单元和高Vth(HVT)单元在表3中给出。结论是在SVT单元/ HVT单元哪一个表明标准Vth点单元的主要性质划分的高Vth单元的形式给出。因此,本设计采用更高的性能和稳定性的标准阈值电压的MOSFET的位单元。低泄漏技术可以有效地降低较大的漏电流。

- 读写分离和变容定时电路

由于在先进工艺技术的大型工艺变化,SRAM的关键是时序控制,是为了实现高速度和低功耗[10,11]。定时控制必须适应不同的PVT条件下的选择性单元最坏情况下的延迟。该复制位单元和位线技术经常被使用[ 10 ]。在现实中,过程的变化,可以解决使用的最坏情况下的设计规范限制[ 12 ]。这导致电路负载过大,从而降低性能和能量。一种数字复制位线延迟技术被提出,以减少过程变化引起的变化[ 11 ]。它可以减少内模内的复制位单元的变化,但可能会产生额外的时序变化的定时乘法器电路和其他变化。本设计采用可编程定时电路与嵌入式BIST,其利用的复制单元的可编程计数跟踪随机过程基于BIST测试结果而变化。在不同的电源电压和温度下,复制位单元的延迟可以跟踪比正常的位单元的延迟。此外,为了更低的功耗,还采用了读写分时控制方法。

4.1. 读写分时控制

图6显示读写分时控制方案和阵列写电流比较,采用分时控制。在不分时控制下,通过读操作的要求决定了字线激活的宽度。根据模拟,需要当不同的电压的激活位线大于150个,所需的字线激活的宽度是至少0.57纳秒,而只有0.32纳秒的字线激活的宽度,在写操作是必需的。如图6所示,当采用分时控制方法时,当CMUX为8:1和4:1时时平均写单元阵列电流分别减少30%和20%。在激活字线的非选择位单元8:1 CMUX大于4:1 CMUX,由于读写分定时控制,从而导致降低写入电流。因此,读写分定时控制是更为有效的CMUX变大。

图6 一个读写分时控制方案和20-30%的写入电流减少了分时控制的使用

图7显示了详细的读写电路设计,分时控制和主要波形。如图7所示,该电路的主要波形显示了读写操作下的SRAM。当时钟信号CLK变高时,输出信号是排放到低电压的晶体管NM3和NM4。同时,低电压控制PM2或PM3活性通过读取延迟块或写延迟,导致了转向高电压。当输出是高水平时,PM2和PM3立即关闭,要么NM3和NM4也同时关闭。输出保持其高水平通过交叉耦合逆变器INV1。其结果是,低电压脉冲宽度的输出是由读延迟或写入延迟决定。

图7 读写分时定时控制电路设计和波形

由于晶体管的大局部失配与工艺技术的缩放,延迟块的延迟变化变得更大。为了抑制过程的变化,通常使用超大的时序控制电路,它的存在降低了SRAM的性能和能量。因此,设计变容读取延迟和写入延迟块是非常重要的,可用于实现高速和低功耗存储器[11]。 为了解决这个问题,作为本文的创新点之一,一个可编程定时控制电路与嵌入式BIST是随着电路设计而被讨论。

4.2. 常规延时控制电路

图8显示了一个传统的定时复制电路及其信号波形[ 10 ]。复制的位线和复制位单元被配置为复制的正常位线电容和放电电流。首先,复制位线(RBL)预充电到VDD。然后,字线(WLL)被激活和复制位线位的细胞数固定排放。在同一时间,正常选择的位线也被由访问的位单元排出。当RBL排放到VDD/2时,△VBL被定义为选定的位线之间的电压差。

图8 传统定时复制电路及其波形

图9显示了△VBL作为不同的电源电压函数的200Monte Carlo模拟结果。它假定为逆变器逻辑感阈值电压是VDD/2。当供电电压为高(VDD=1.2 V)和复制的单元数是固定时,这意味着,△VBL的标准偏差

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[147561],资料为PDF文档或Word文档,PDF文档可免费转换为Word