英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

一种改进的单脉冲雷达

角度测量数据对准方法

史庆占,张德平,柯克雷,奈昌元

国防科技大学电子科学与工程学院,中国

摘要:准确测量目标的距离和角度是实时跟踪目标的重要部分。 目标与雷达之间的距离可以通过目标回波的时间延迟来计算。 同时,目标角度测量有各种成熟的算法。 单脉冲角测量是一种常用的方法。 在单脉冲雷达系统中,我们使用sum channel和diff channel采样的数据来计算目标角度信息。 所以通道采样数据对角度计算很重要。 总和通道和差分通道之间的相位一致性是必不可少的条件。 在基于高速AD转换器和FPGA的PCB板上,多个差分对数据线的长度通常不相等,这将导致到FPGA逻辑的到达时间不同。 这将导致不同数据通道之间的相位偏移。 在这种情况下,它不会精确地进行角度测量。 在此背景下,本文提出了一种基于FPGA中先进先出(FIFO)的自动数据对齐方法。 本文详细介绍了该方法,并对比了数据结果。 结果验证了有效性。 该方法已成功用于雷达系统。

1.介绍

随着集成电路技术的发展,电路设计的规模迅速增加,雷达系统设计的难度也越来越大[1]。 在现代雷达系统中,很多高性能AD采样芯片和数字信号处理器(DSP)以及现场可编程门阵列(FPGA)器件被应用于雷达系统的设计[2]。 为了获得目标的角度和速度信息,采样系统通常使用多个通道来获得原始回波信号。 因此,不同信道的采样数据一致性对于后续的信号处理非常重要[3,4]。 在单脉冲测角雷达系统中,如果不同通道采样数据的时延不一致,就不能得到目标的角度信息。 在此背景下,本文提出了一种基于FIFO机制的数据对齐方法。 与传统的利用FPGA内部IODELAY原语调整数据时延的方法相比,该方法具有更高的稳定性和可靠性。

本文的内容和结构安排如下:第二部分给出了系统架构,并介绍了ADC的通道采样数据的特点。 第3部分详细介绍了采样数据的对齐方法。 对齐结果在第4部分中给出。最后,对全文进行总结并给出结论。

2.系统体系结构和采样数据选择动作

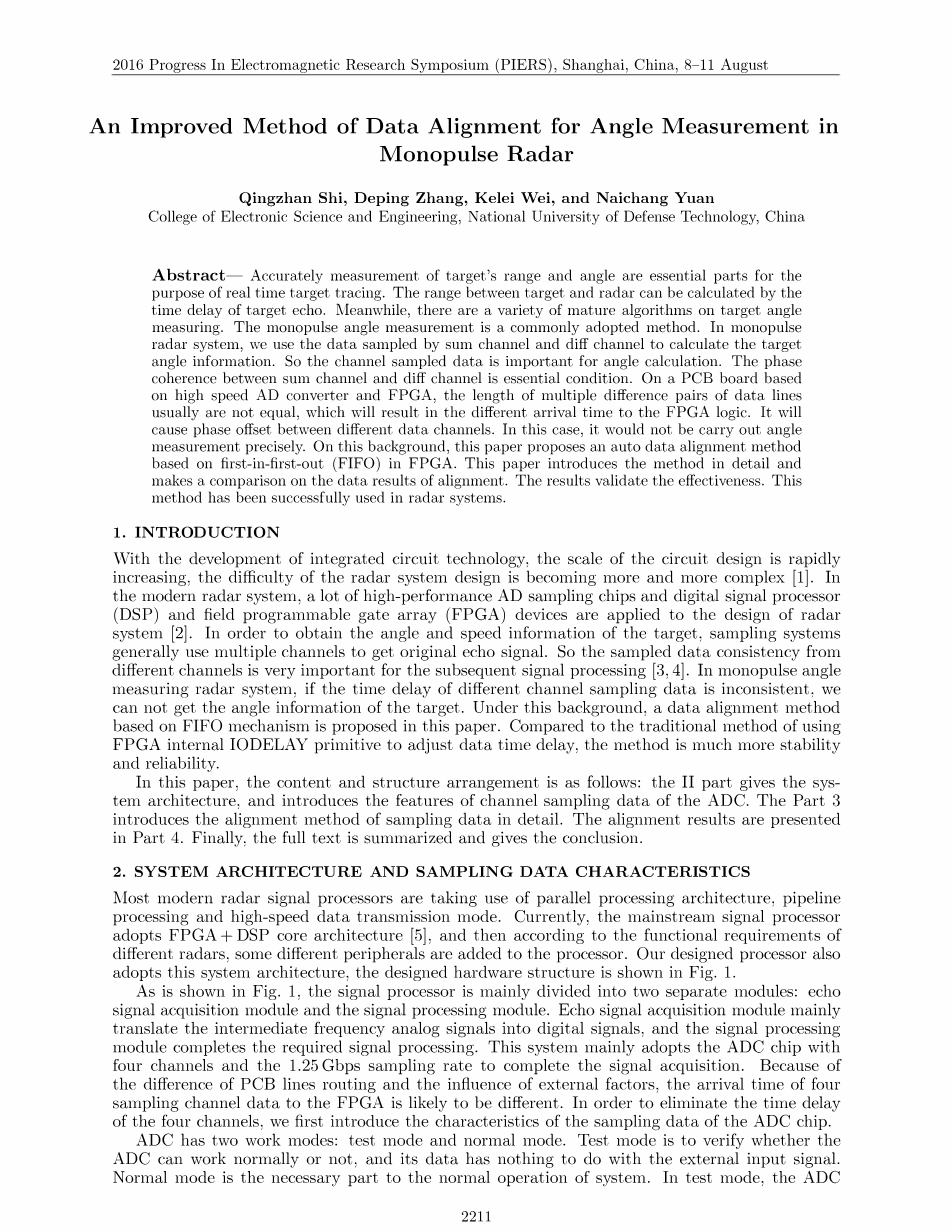

大多数现代雷达信号处理器都采用并行处理架构,流水线处理和高速数据传输模式。 目前,主流信号处理器采用FPGA DSP内核架构[5],然后根据不同雷达的功能要求,将一些不同的外设添加到处理器中。 我们设计的处理器也采用该系统架构,设计的硬件结构如图1所示。

图1 系统硬件结构

如图1所示,信号处理器主要分为两个独立的模块:回波信号采集模块和信号处理模块。 回声信号采集模块主要将中频模拟信号转换为数字信号,信号处理模块完成所需的信号处理。 该系统主要采用四通道ADC芯片和1.25 Gbps采样率完成信号采集。 由于PCB线路布线的不同和外部因素的影响,四个采样通道数据到FPGA的到达时间可能会有所不同。 为了消除四个通道的时间延迟,我们首先介绍了ADC芯片采样数据的特点。

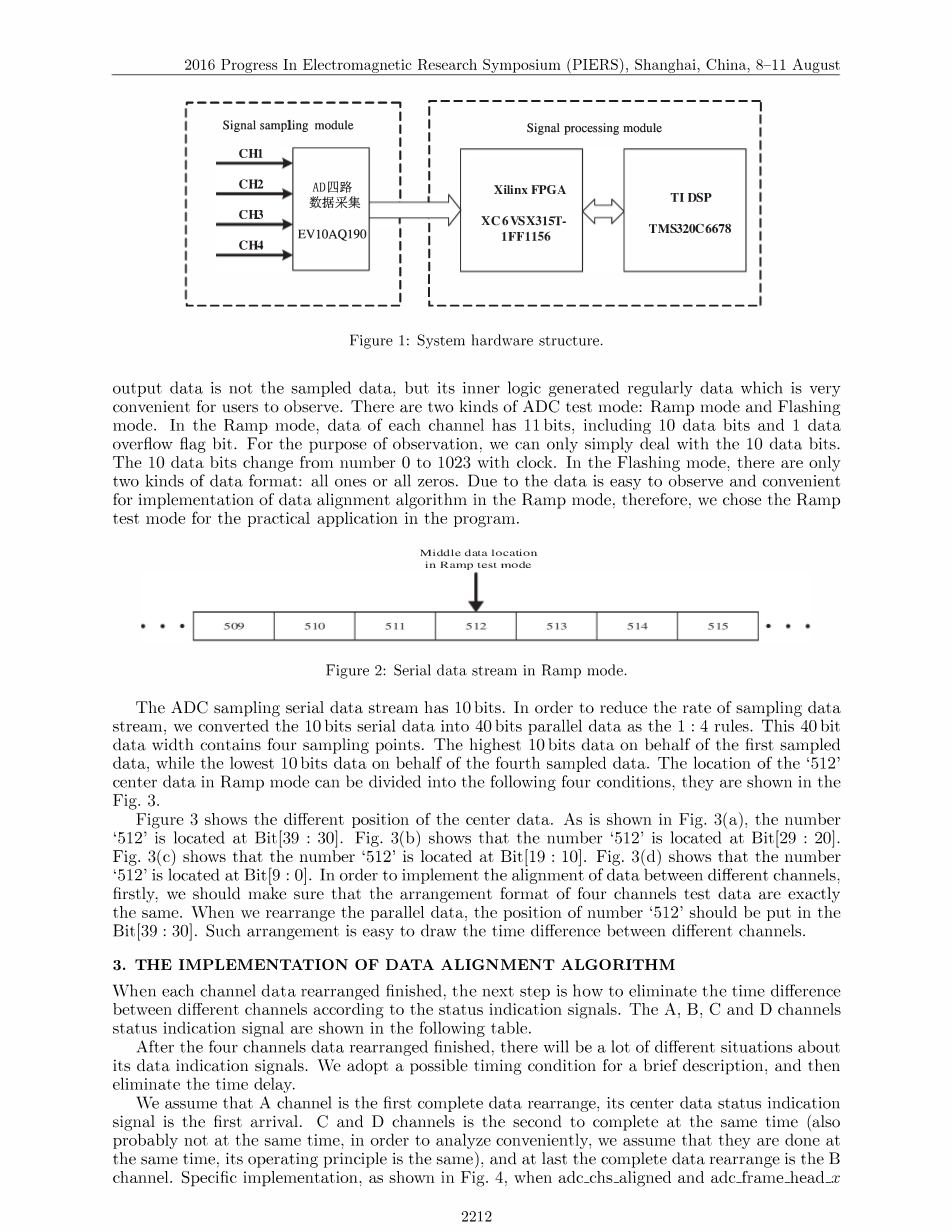

ADC有两种工作模式:测试模式和正常模式。 测试模式是验证ADC是否能正常工作,其数据与外部输入信号无关。 正常模式是系统正常运行的必要部分。 在测试模式下,ADC输出数据不是采样数据,而是其内部逻辑定时生成的数据,非常方便用户观察。 有两种ADC测试模式:斜坡模式和闪烁模式。 在斜坡模式下,每个通道的数据有11位,包括10个数据位和1个数据溢出标志位。 为了观察的目的,我们只能简单地处理10个数据位。 10个数据位随着时钟从数字0变为1023。 在闪烁模式下,只有两种数据格式:全部为一或全部为零。 由于数据易于观察,便于在斜坡模式下实现数据对齐算法,因此我们在程序中选择了斜坡测试模式进行实际应用。如图2。

图2 斜坡模式下的串行数据流

ADC采样串行数据流有10位。 为了降低采样数据流的速率,我们将10位串行数据转换为40位并行数据作为1:4规则。 这40位数据宽度包含四个采样点。 代表第一个采样数据的最高10位数据,代表第四个采样数据的最低10位数据。 R模式下512中心数据的位置可以分为以下四个条件,如图3所示。

图3显示了中心数据的不同位置。 如图3(a)所示,数字512位于位[39:30]。 图3(b)显示数字512位于位[29:20]。 图3(c)显示数字512位于位[19:10]。 图3(d)显示数字512位于位[9:0]。 为了实现不同通道间的数据对齐,首先要确保四路测试数据的排列格式完全一致。 当我们重新排列并行数据时,数字512的位置应放在位[39:30]中。 这样的安排很容易画出不同频道之间的时差。

3.数据对齐算法的实现

当每个通道数据重新排列完成后,下一步是如何根据状态指示信号消除不同通道之间的时间差。 A,B,C和D通道状态指示信号如下表所示。

四路数据重新排列完成后,其数据指示信号会有很多不同的情况。 我们采用可能的时间条件进行简要描述,然后消除时间延迟。

假设A通道是第一个完整的数据重新排列,其中心数据状态指示信号是第一个到达。 C和D通道是同时完成的第二个通道(也可能不同时,为了便于分析,我们假设它们在同一时间完成,其工作原理相同),并且最后完整的数据重新排列是B通道。 具体实现如图4所示,当adc_chs_aligned和adc_frame ead-x同时较高,立即声明adc_ch_x_align_fifo_wLen信号(x表示a,b,c或d)并在置位后保持高电平。

图3 斜坡模式下512个中心数据的位置。(a)位于位[39:30]。(b)位于位[29:20]。 (c)位于[19:10]。(d)位于位[9:0]。

图4 不同通道的状态指示信号

当四个通道FIFO包含一定数量的数据时,我们同时确认四个FIFO的读取信号并保持高电平。 如图5所示,通道A中FIFO数据的深度为N 2,通道B中FIFO数据的深度为N,通道C和D中FIFO数据的深度为N 1。图5在时序关系上完全对应于图4。 从图5可以看出,在从FIFO中读取数据之前,每个FIFO中的第一个数据是每个通道位置数据{512,513,514,515}的中心。 当我们连续地从四个FIFO中读写数据时,四个通道中的数据量保持不变。 这是不同通道之间数据对齐的算法。

图5不同渠道的数据量

4.实验测试

为了对ADC进行正确配置并处理采样数据,我们设计了一个简单的小型FPGA测试程序,主要用于验证ADC工作在测试模式下,数据在斜坡模式下对齐。 图6示出了在斜坡测试模式中对准之前和之后的四个通道数据比较的结果。 正如我们所看到的,在对齐之前在不同通道之间存在固定的时间延迟,而在数据对齐之后时间延迟被消除。

图6 斜坡模式下的数据比较结果。(a)在对齐之前,(b)对齐后

5.结论

由于各种高速ADC采样数据通道的时延不一致,本文提出了一种通道数据自动对齐的方法。 与传统的数据对齐方法相比,该方法简单,稳定,可靠。 实验数据比较结果证明了该算法的有效性。 该方法已成功用于雷达系统。

6.参考文献

1.Flatt,H.,S.Schriegel,J.Jasperneite和F.Schewe,”用于增强具有实时以太网功能的COTS开关ASIC的基于FPGA的方法”,国际会议上的新兴技术和工厂自动化(ETFA),2012年

2.Wu,XD和B.Dai,“基于FIFO的高速AID和DSP之间的接口设计”,北京石油化工学院学报,Vol.14,第12期,26-29,2006年6月

3.Shih,C.-S.,C.-M.Yang和Y.-C.Cheng,”在loT融合网关上没有同步时钟的多时间数据流的数据调整”,2015年IEEE数据科学和数据密集系统国际会议,667-674,2015

4.Jer,LH,E.-G.Siew和S.Egerton,“搜索引擎结果页面的可视化数据对齐”,第二届计算机研究与发展国际会议,141-145,2010

5.Pan,F.S,F.Zhao,J.Xi,and Y.Luo,“基于FPGA和多DSP的并行信号处理系统的实现”,Computer Engineering,Vol.2006年12月第32号,第23号,第247-249号

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[22390],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。