英语原文共 8 页,剩余内容已隐藏,支付完成后下载完整资料

双路256抽头低压数字控制电位计(XDCPtrade;)

ISL23425是易失性,低电压,低噪声,低功耗,256抽头双数字电位器(DCP),带有一个

SPIBustrade;接口。 它集成了两个DCP内核,抽头开关单片CMOS集成电路上的控制逻辑。每个数字电位器均具有一个电阻元件和CMOS开关的组合。 这刮水器的位置由用户通过SPI总线接口。 每个电位计都有一个相关的以直接写入的易失性抽头寄存器(WRi,i = 0,1)

并由用户阅读。 WRi的内容控制着刮水器的位置。 上电时,每个DCP的抽头将始终从中音阶(128抽头位置)开始。低电压,低功耗和小封装ISL23425的特性使其成为电池使用的理想选择操作设备。 此外,ISL23425具有一个VLOGIC引脚允许低至1.2V的总线操作,独立于VCC值。 这允许连接低逻辑电平直接连接到ISL23425,而无需通过电压电平转换器。

DCP可用作三端电位计或用作两端可变电阻,适用于多种应用包括控制,参数调整和信号处理。

应用

bull;电源裕度

bull;整理传感器电路

bull;电池供电仪器的增益调整

bull;射频功率放大器偏置补偿

特点

·每包两个电位器

·256电阻丝锥

·10k 50k或100k总电阻

·SPI串行接口

-没有额外的电平转换器低总线供应

-多个DCP的菊链

最大电源电流,无串行总线活动(支持)

- 4micro;A @ VCC and VLOGIC = 5V

- 1.7micro;A @ VCC and VLOGIC = 1.7V

关机模式

-强制DCP进入端到端开路,RWi为内部连接到RLi

-通过断开DCP来降低功耗电路中的电阻

电源

-VCC = 1.7V至5.5V模拟电源

-VLOGIC = 1.2V至5.5V SPI总线/逻辑电源

抽头电阻:70典型值@ VCC = 3.3V时,

bull;开机预设为中档(128分接位置)

bull;扩展的工业温度范围:-40°C至 125°C

bull;14 Ld TSSOP或16 Ld micro;TQFN封装

bull;无铅(符合RoHS)

图2. VREF调整

RH1

-

VREF_M

1 DCP OF ISL23325

RW1

ISL28114

RL1

抽头位置(十进制)

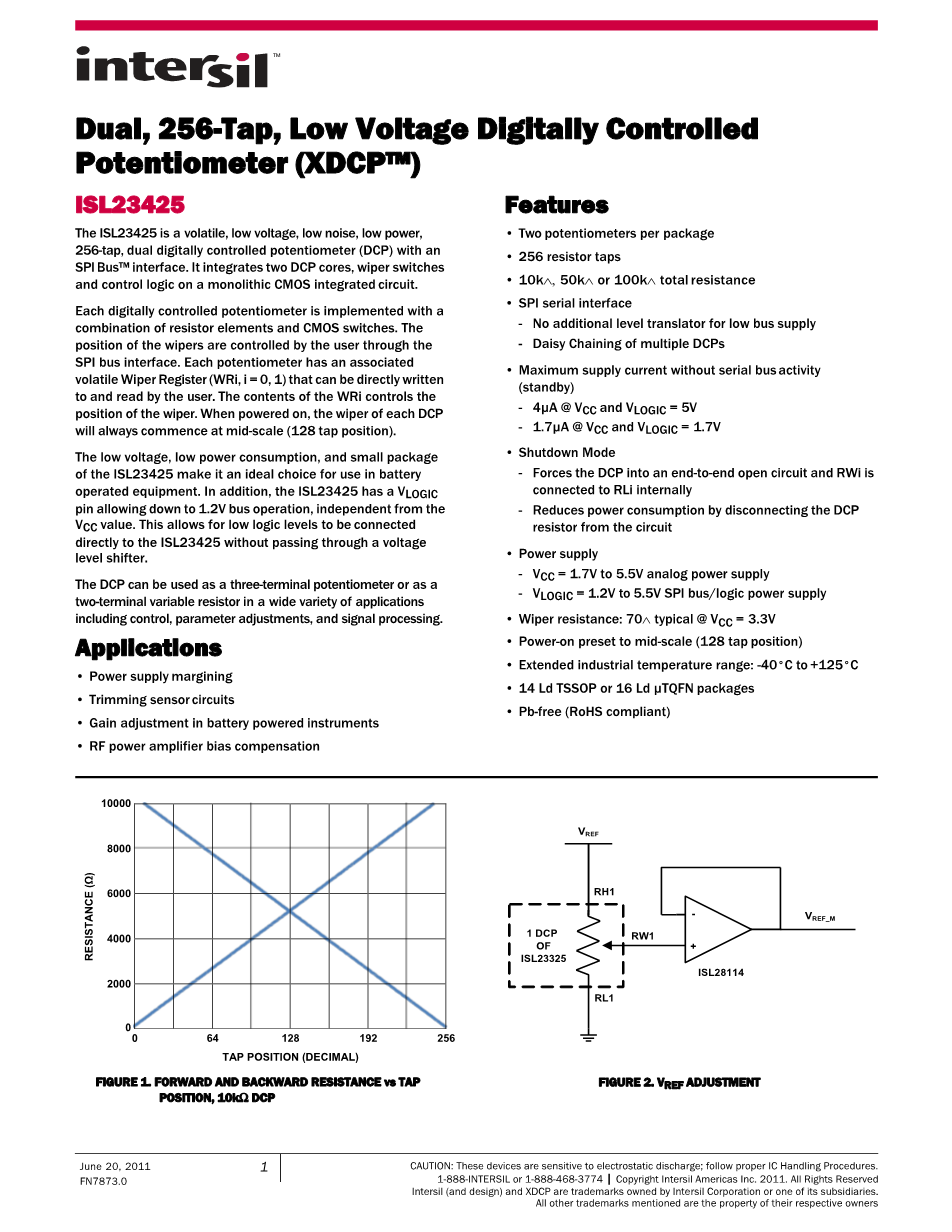

图1.前进和后退电阻与TAP的关系位置,10kOmega;DCP

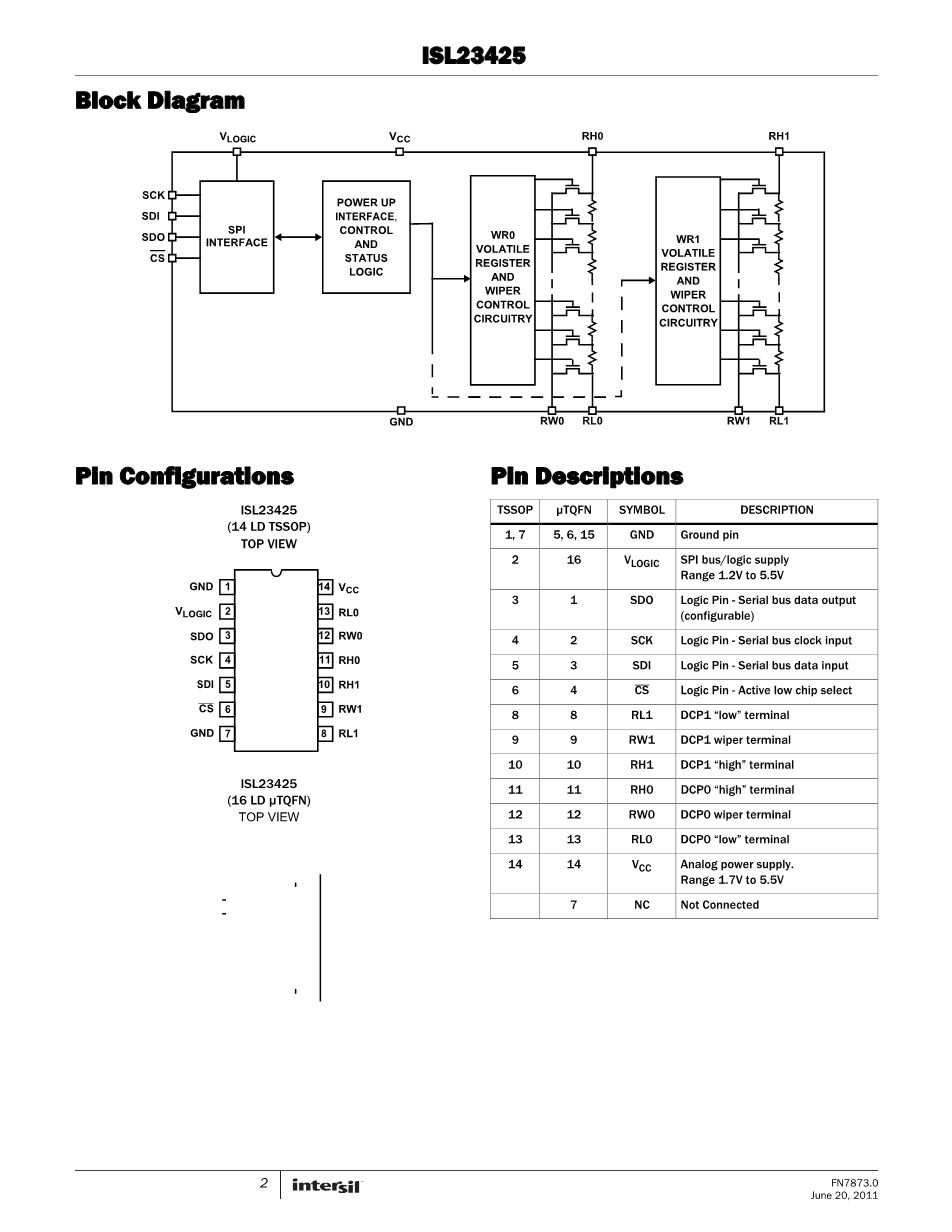

框图

SCK SDI SDO

CS

POWER UP INTERFACE, CONTROL AND STATUS LOGIC

WR1 VOLATILE REGISTER AND WIPER CONTROL CIRCUITRY

WR0 VOLATILE REGISTER AND WIPER CONTROL CIRCUITRY

SPI INTERFACE

引脚配置 引脚说明

ISL23425(14 LD TSSOP)

顶视图

SL23425(16 LD micro;TQFN)

顶视图

串行数据输出(SDO)

SDO是串行数据输出引脚。 在读取周期内,数据位在串行时钟SCK的下降沿移出,并在随后的SCK上升沿提供给主机。

通过ACR [1]位配置输出类型,以进行推挽或漏极开路操作。 该引脚的默认设置为推挽式。 开漏输出操作需要一个外部上拉电阻。 当CS为高电平时,SDO引脚处于三态(Z)或

高三态(Hi-Z)取决于所选的配置。

芯片选择(CS)

CS LOW使能ISL23425,将其置于有功功率模式。 上电后,开始任何操作之前,需要CS上从高电平到低电平的转换。 当CS为高电平时,ISL23425被取消选择并且SDO引脚处于高阻态,并且器件将处于待机状态。

VLOGIC

逻辑控制部分的数字电源。 它提供用于1.2V至5.5V串行总线操作的内部电平转换器。 使用与I2C逻辑源相同的电源。

操作原理

ISL23425是一种集成了两个DCP及其相关寄存器和SPI串行接口的集成电路,该串行接口提供了主机与电位计之间的直接通信。电阻器阵列由串联的单个电阻器组成。 一个电子开关位于阵列的两端,且位于每个电阻器之间,该开关将那个点的电位传递给抽头。当刮水器更改分接头位置时,设备上的电子开关以“先断后合”模式工作。在加电和正常工作期间,在任何情况下,任何DCP引脚RHi,RLi或RWi的电压均不得超过VCC电平。VLOGIC引脚是逻辑控制数字电源的端子。 它应使用与SPI逻辑源相同的电源,允许与各种微控制器,并且独立于VCC级别。 这在主电源电平低于DCP模拟电源电平的系统中非常重要。

DCP说明

每个DCP均由电阻器元件和CMOS开关组合而成。 每个DCP的物理端均等效于机械电位计的固定端子(RHi和RLi引脚)。 DCP的RWi引脚连接到中间节点,等效于机械电位计的抽头端子。 DCP中抽头端子的位置由8位易失抽头寄存器(WRi)控制。 当DCP的WR包含全零时(WRi [7:0] = 00h),其抽头端子(RWi)最接近其“低”端子(RLi)。 当DCP的WRi寄存器全为(WRi [7:0] = FFh)时,其抽头端子(RWi)最接近其“高”端子(RHi)。 随着WRi的值从全零开始增加(0)到全1(十进制255),抽头从最靠近RLi的位置单调移动到最靠近RHi的位置。同时,RWi和RLi之间的电阻单调增加,而RHi和RWi之间的电阻单调减小。在ISL23425通电时,两个WRi都重置为80h(十进制128),这将RWi置于RLi和RHi之间的中心。可以使用SPI串行接口直接读写WRi,如以下各节所述。

记忆体描述

ISL23425包含三个易失的8位寄存器:抽头寄存器WR0,抽头寄存器WR1和访问控制寄存器(ACR)。ISL23425的存储器映射如表1所示。地址为0的抽头寄存器WR0包含DCP0的当前抽头位置;其地址为0。 地址1的抽头寄存器WR1包含DCP1的当前抽头位置。 地址10h处的访问控制寄存器(ACR)包含表2中所述的信息和控制位。

表1.内存映射

|

地址 (十六进制) |

易失性注册 名称 |

默认设置 (十六进制) |

|

10 |

ACR |

40 |

|

1 |

WR1 |

80 |

|

0 |

WR0 |

80 |

表2.访问控制寄存器(ACR)

|

BIT # |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

名称/值 |

0 |

SHDN |

0 |

0 |

0 |

0 |

SDO |

0 |

SDO位(ACR [1])配置SDO输出引脚的类型。 推挽输出的SDO位默认值为0。 对于某些应用,可以将SDO引脚配置为漏极开路输出。 在这种情况下,需要一个外部上拉电阻,请参考第6页的“串行接口规范”。

关机功能

SHDN位(ACR [6])同时禁用或启用所有DCP通道的关闭模式。 当该位为0时,即,每个DCP被迫端到端开路,并且每个RW通过2kOmega;串行电阻器与RL短路,如图25所示。SHDN位的默认值为1。

图25.关机MOD中的DCP连接

2kΩ

当设备进入关机状态时,所有当前的DCP WR设置都会保留。 当设备退出关闭状态时,在短暂的建立时间后,抽头将返回到先前的WR设置(见图26)。

POWER-UP

MID SCALE = 80H

USER PROGRAMMED

AFTER SHDN

SHDN ACTIVATED

SHDN RELEASED

WIPER RESTORE TO THE ORIGINAL POSITION

0

SHDN MODE

TIME (s)

图26.关断模式刮水器响应

SPI串行接口

ISL23425支持SPI串行协议(模式0)。通过SDI输入和SDO输出访问器件,数据在SCK的上升沿移入,在SCK的下降沿移出。 与ISL23425通信期间,CS必须为低电平。 SCK和CS线由主机或主机控制。 ISL23425仅作为从设备运行。

SPI接口上的所有通信都是通过首先发送数据的每个字节的MSB来进行的。

协议约定

SPI协议包含指令字节,后跟一个或多个数据字节。 一个有效的指令字节包含作为三个MSB的指令,以及以下五个寄存器地址位(见表3)。

发送到ISL23425的下一个字节是数据字节。

|

BIT # |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

I2 |

I1 |

I0 |

R4 |

R3 |

R2 |

R1 |

R0 |

表4包含ISL23425的有效指令集。

如果[R4:R0]位为零或一,则对WRi寄存器进行读或写。 如果[R4:R0]为10000,则操作针对ACR。

|

INSTRUCTION SET |

OPERATION |

|||||||

|

I2 |

I1 |

I0 |

R4 |

R3 |

R2 |

R1 |

R0 |

|

|

0 |

0 |

0 |

X |

X |

X |

X |

X |

NOP |

|

0 |

0 |

1 |

剩余内容已隐藏,支付完成后下载完整资料 资料编号:[259606],资料为PDF文档或Word文档,PDF文档可免费转换为Word |

|||||

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。