英语原文共 10 页,剩余内容已隐藏,支付完成后下载完整资料

基于sum;-delta;模数转换器的数字音频传感器自适应读出ASIC

摘要

数字音频传感器已被应用于微型手机嵌入式便携式电子设备中。摘要介绍了一种数字音频传感器的混合信号自适应读数ASIC,其中包括可编程增益放大器、开关电容式sigma-delta调制器、数字信号处理和电源管理电路。数字部分包括一个数字低通滤波器,一个数字增益补偿和一个数字自动增益控制器。该系统的明显优点是同时获得高信噪比(SNR)和带宽输入范围。此外,还实现了正常的操作模式和睡眠模式,以灵活的解决当前预算问题。ASIC是在一个0.18-umCMOS工艺中制造的。实验结果表明,期望自适应读出函数在94到136 dB SPL的输入范围。在正常模式下,在1 kHz 94 dB SPL输入下,系统SNR为68 dB(a-加权),在600uA下实现。此外,保证了136 dB SPL的令人印象深刻的声过载点(AOP)。在待机状态下,获得了电流小于20 uA的睡眠模式,从而延长了电池寿命。与其他现有的解决方案相比,这种自适应读出ASIC显示了可实现的SNR、AOP和数字音频传感器的当前预算的最佳组合。

关键字: 音频传感器 自适应 AGC PGA Sigma-delta

- 简介

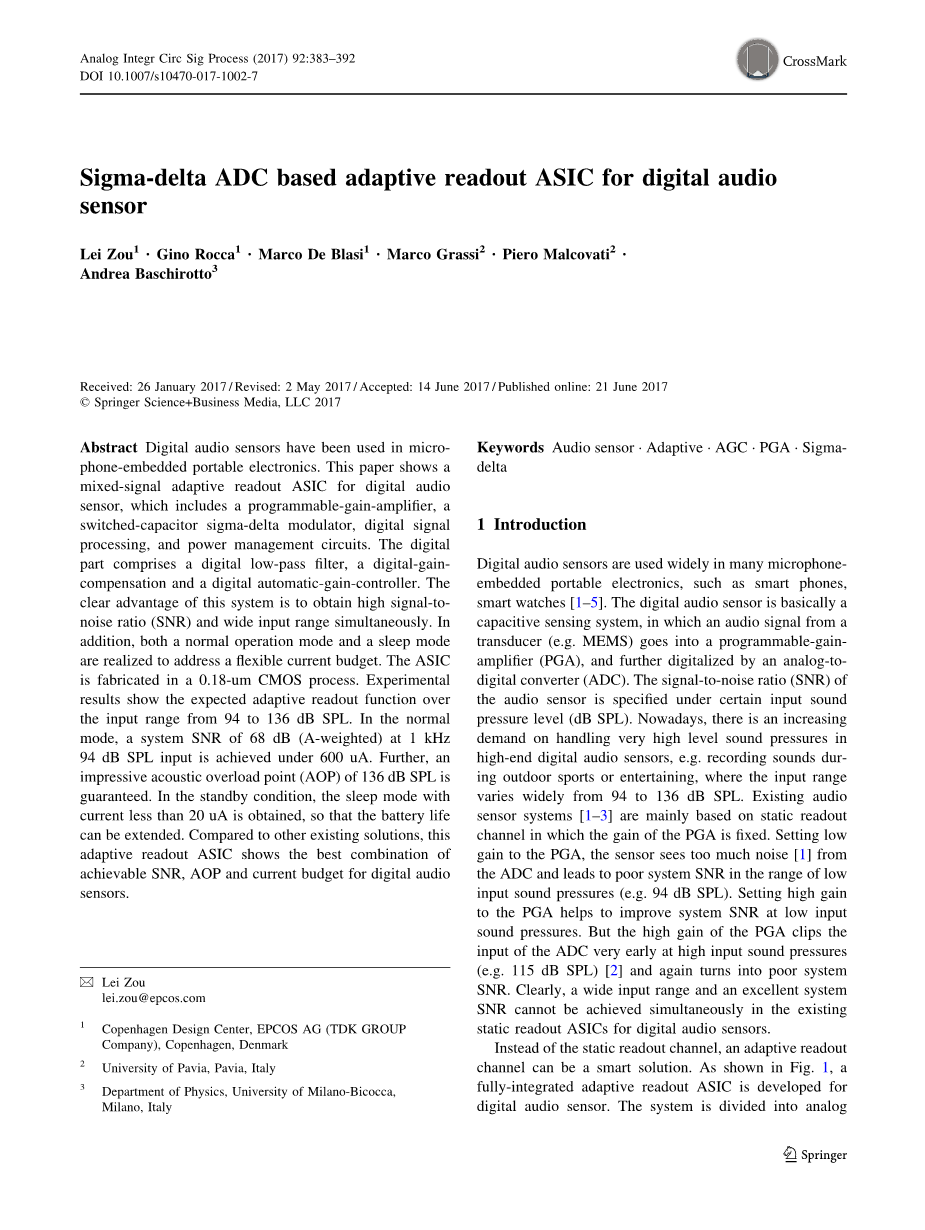

数字音频传感器广泛应用于许多麦克风——嵌入式便携式电子设备,如智能手机、智能手表1-5。数字音频传感器基本上是一种电容感应系统,在这种系统中,来自传感器(如MEMS)的音频信号进入可编程增益放大器(PGA),并通过模拟-数字转换器(ADC)进一步数字化。音频传感器的信噪比(SNR)是在一定的输入声压级(dB SPL)下指定的。如今,在高端数字音频传感器中,对高水平声音压力的需求越来越大,例如,在户外运动或娱乐中记录声音,输入范围在94到136 dB SPL之间有很大的差异。现有的音频传感器系统1-3主要基于静态读出通道,在这个通道中,PGA的增益是固定的。将低增益设置为PGA,传感器从ADC中看到太多的噪声,并导致低输入声压力范围内的系统SNR(例如94分贝SPL)。在低输入声压力下,为PGA设定高增益有助于改善系统的SNR。但是,PGA的高增益在高输入声压力(如115 dB SPL)2的早期,就会将ADC的输入信号转换为糟糕的系统SNR。显然,在现有的数字音频传感器的静态读数asic中,不能同时实现一个广泛的输入范围和一个优秀的系统SNR。与静态读出通道不同的是,自适应读数通道可以是一个智能解决方案。如图1所示,为数字音频传感器开发了一个完整的自适应读数ASIC。系统被分为模拟信号处理,数字信号处理(DSP)和电源管理单元(PMU)。模拟信号的处理部分包括一个PGA,一个抗混叠滤波器(AAF)和一个调制器。DSP部分包括一个数字低通滤波器,一个数字增益补偿(DGC)和一个数字自动增益控制器(AGC)。PMU包括一个带隙参考,一个低退出的调节器(LDO),请参考电压缓冲器和频率检测器。

图1 用于数字音频传感器的全集成自适应读数ASIC

频率检测器监控采样开关在正常模式和睡眠模式之间的切换,以延长电池寿命。频率检测器监测取样。

在混合信号实现的优点下,该系统可以通过数字电路进行优化。与模拟电路相比,数字电路的设计挑战了供应的变化。根据输入模拟信号的信号电平(即峰值振幅),PGA的增益是不同的。对于小的输入级别,将会有很大的增益被设置为PGA,而小的增益被选择为大的输入级别。数字AGC检测输入信号电平并相应地调整Ga。理想情况下,AGC反馈回路应该立即调整Ga,以避免在PGA的输出中出现剪切和失真。但是AGC循环本身有一个延迟。延迟是由调制器、数字低通滤波器和数字AGC延迟的总和。对于快速响应,应该尽量减少延迟。

调制器的输出是脉冲密度调制(PDM)信号。在这个系统中,只有峰值振幅是AGC感兴趣的,因此全分辨率的数字信号和基带采样时钟不是必要的。因此,可以避免使用一种十进制滤波器(低通和低采样),这通常是作为冷杉过滤器实现的,可以避免大量的点击。这有助于减少AGC循环的延迟。摘要介绍了一种具有短延时和较少区域成本的低通数字贝塞尔滤波器,而不是十进制滤波器。然后,PDM信号可以是低-通过过滤,在30 kHz的截止时间,以20位二进制字的形式重建PGA的输出振幅。现在,数字AGC可以通过比较二进制单词和预定义的上下限和较低阈值来调整Ga。系统输入-引用的噪声计算在(1)中,

(1)

在其中,代表是系统输入-引用的噪声,是PGA的输入-引用噪声,而是调制器的输入-引用噪声。

(2)

系统SNR是在(2)中计算的,其中Vsignal代表输入模拟信号的RMS电压。对于小的Vsignal,在PGA中选择了大的Ga,所以Vn,总是可以得到较小的SNR。对于大型Vsignal,应该选择小的Ga,但是这增加了Vn的系数。然而,大的Vsignal仍然可以得到高SNR。因此,自适应读出信道能够同时实现一个优秀的系统SNR和广泛的v信号。最大输入电平通常被解释为声过载点(AOP),它是输入信号电平,系统的信号-噪声-失真比(SNDR)等于20分贝。在这个自适应读数ASIC中,可以预期高系统的SNR和高的AOP。

我们希望音频读出ASIC的灵敏度是一个时不变的参数,因此给定的声压级只会产生一个唯一的输出信号。这意味着一个恒定的读出通道增益。因此,PGA获得的收益是通过减少相同的收益来补偿的。由于调制器的输出是数字的,

Ga的变化是在DGC中得到补偿的,它是由增益系数0-30 dB实现的。最终,整个音频读出通道增益为

(3)

在DGC中,数字增益Gd等于——Ga,这样即使模拟输入信号级别,统一的通道的增益也始终保持不变。由于数字逻辑操作的巨大噪声免疫,数字电路的器件噪声可以被忽略,这使得(1)当DSP被计入读数通道时仍然有效。

第2节描述了PGA的实施情况和抗锯齿过滤器。

第3部分描述了调制器的实现。第4节描述了PMU块的设计。第5节展示了测量结果。结论在第6节中给出。

- PGA和AAF

PGA作为一个电容感应接口,它放大了转导信号并驱动了下一个电路阶段。PGA是一个完全不同的反馈放大器,增益是由输入电阻器和反馈电阻器设置的。然而,输入电阻的是有限输入,从输入电阻中得到一个额外的源-跟随器来分离出从降解中产生的信号。在这个设计中,图2所示的PGA是基于仪器放大器的拓扑结构。它具有非常高的输入阻抗和较少的共模反馈(CMFB)。传感器的输出信号通常缺少一个已定义的通用模式电压。因此,PGA的输入-单模电压是由一个直流电平建立的,目标是快速的沉降时间和低失真,并且在图中没有显示出来。PGA增益Ga由电阻R1和R2决定,而R1的电阻则由数字AGC控制。

图2 PGA和AAF

(4)

图中还显示了输入信号级别的增益设置。增益步骤不应该太大,不能引入明显的故障,这是可以察觉的。PGA的总谐波失真(THD)为0.01%,为94分贝,并随输入水平的上升而上升。图3显示了PGA、Vn、PGA等对增益设置的输入-引用噪声。对R1和R2的电阻的选择必须考虑热噪声和当前的预算。在高增益的范围内,大R1带来了更多的PGA的输出噪声,在取余之后,根据高增益,Vn,PGA仍然在2.55 uVrms。

AAF是由聚电阻和MOS电容制造的一阶低通滤波器。低通滤波器的截止频率为237 kHz。截止频率的选择是基于两个问题。首先,输入信号带宽的衰减(20-20 kHz)小于0.1 dB。其次,0.5 Fs(Fs是采样时钟频率为3.6 MHz)的衰减大约是15分贝。事实上,传感器本身可以在一定的带宽上衰减频率组件。因此,AAF不需要为超过0.5 f的频率提供深度衰减。此外,AAF还有助于减少在PGA的增益转换过程中产生的故障。在PGA中,偏置发电机电路产生了必要的偏置电流。在睡眠模式下,对每个放大器的偏置电流都被频率检测器的模式信号所禁用。

图3 模拟Vn,PGA和Ga

- SC Sigma;Delta; 调制器

调制器向DSP提供PDM信号。与其他类型的ADCs[7]相比,ADC适用于中低速度和高分辨率的应用程序。与使用CT调制器4相比,开关电容(SC)调节器更受青睐,因为它不太依赖于过程变化和时钟抖动。

3.1 调制器拓扑

图4中所示的单回路二阶SC调制器拓扑实现。首先,这种拓扑对OTA增益、开关电阻和电容错配不太敏感。其次,这种拓扑由于1位比较器和1位DAC具有固有的线性关系,并且在不增加额外设计工作的情况下显示了良好的稳定性和饱和度恢复。第三,从理论上讲,拓扑可以支持高达92分贝的SNR,它的采样率为90度(OSR),由(5)式可以知道,

(5)

尽管3或4阶调节器可以用更少的OSR到达相同的SNR,但调制器的延迟延迟会延长AGC循环延迟。与此同时,需要更多的芯片区域和设计工作来确保稳定和饱和的恢复。

图4.二阶单回路SC调制电路

图5.(Z)的极点和零点

噪声传递函数(NTF)在图5中绘制,而信号传输函数(STF)就是简单的统一。这些系数用MATLAB 进一步扩展。最后,带有设备噪声的晶体管级模拟启用了调制器,并且为这个SC调制器获得了84分贝的峰值SNR(a-加权)。

在这个调制器中不使用双采样的SC集成商。尽管双采样的SC积分器减少了相同SNR的一半必要大小的C1,但是该技术引入了路径不匹配、额外的噪声折叠和更多的开关。集成商中的电容器产生kt/c噪声,而采样帽C1是主要的噪音贡献者。为了估计C1的大小,我们可以先假设OTA是无噪声的,然后使用下面的方程,

(6)

为SNR,OSR和全尺寸输入电压,VFS,125fF被选为最小的电容器用于多重化系数。在过程和温度角下,这个上限值足够大,可以防止SNR的损耗小到足以支持期望的旋转速度和获得的带宽产品(GBW)。在SIMULINK 12中,在非理想积分仪的行为模型中包含了大量的速率和GBW,并且可以通过在二阶调制器上的模拟来轻松优化。

3.2 全差分运算跨导放大器

图6给出了集成电路中全差分运算跨导放大器。使用了带有SC CMFB的折叠串联放大器。只有一个CMFB电路。这比类ab放大器的效率更高,因为在这里使用了两个CMFB。此外,CMFB循环基本上是单级,因此稳定性很容易获得。第一个OTA的输入-被引用的噪声不是由mod-循环系统所决定的。特别地,采样的噪声混叠是不可避免的。全谱集成的输入-引用噪声首先被OSR分割,然后进一步关闭——循环引用来获得第一个集成上的内带噪声。在没有直升机或自动-零技术的情况下,扩大输入晶体管是一种有效的方法,可以减少偏移量(可能不是对a-加权SNR的关注),同时减少OTA的闪烁噪声和热噪声。可以忽略来自串联阶段和CMFB电路的噪声贡献。此外,为了最大程度地减少由于不匹配而导致的理想微分结构的偏差,重要的是为OTA提供通用的质心布局。可调的电流源I1——I5由频率检测器提供的模式信号控制。在睡眠模式下,电流源被关闭。

图6 全差分运算跨导放大器电路

3.3 闩锁比较器

如图7所示,使用了一个1位高速的比较器。在再生门闩上的SR门闩有助于保持比较结果出来,在整个时钟周期内。输入偏移量和比较器的输入-被引用的噪声被调制器的回路深深影响,这样它们的影响就可以忽略不计了。这比一个连续的近似ADC要优越,在这里,比较器的偏移量和噪声应该被仔细考虑。

图7 门闩比较器电路

- 电源管理单元

专用于调制器的PMU包括频率检测器、LDO、带隙参考和参考电压缓冲器。直接的电池连接能力得到支持,电池的供应范围从1.62到3.6 V,而名义上的电池供应是1.8V。

4.1 频率检测器

频率检测器被设计成一个数字频率检测器。用单独的计数器来计算输入采样时钟的边缘和参考时钟。 参考时钟是由内置的五个阶段环振荡器产生的。频率检测器输出模式,在时钟频率=3.6兆赫时,正常模式的“11”,当时钟频率300 kHz时,睡眠模式的“00”。摘要数字频率检测器具有较低的平均电流和较低的硬件成本。

4.2 带隙基准稳压器

图8显示了无能力的LDO。LDO通过增加带隙输出电压Vref来生成内部供应VDD。误差放大器使用一个折叠的cas-码放大器。带隙参考的示意图是从标准的带隙拓扑结构(基于cmos-兼容双极晶体管和反馈放大器)进行的。Vref的温度独立性是通过对基本发射极电压Vbe求和而得到的,它的差值乘以电阻率。为了提供足够大的循环增益并最小化输出噪声,带宽的电流得到了优化。未修剪的tem-温度系数(TC)和Vref的精度是15 ppm/c(最坏的情况)和1.2%(3)。带隙参考的电源拒绝(PSR)是95分贝,100赫兹,这是直接连接到电池的。通过良好的电阻调整来校准Vbe的过程变化,进一步提高了准确性或TC。

图8 简易无电容LDO电路

由于LDO的电容输出负载较低,节点VDD的第二根在Cg上接近第一极。本文介绍了一种用于频率补偿的极化消除技术。出现零值的原因是由一个电容C1和一个电阻R3并联产生的,它可以计算由第二极引起的相移,然后达到一个稳定的单极点近似。输出LDO的噪声被看作是对完全不同的在线旅行社的一种常见模式信号,因此它的效果是一个小问题。在电压1.8V以下的情况下,LDO输出必须得到良好的调节,以保持足够高的PSR。因此,传递晶体管的宽比被设置为3000/0.6,这就导致了一个低的退出电压,这个电压小于50 mV,通过

全文共9429字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[17392],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。