英语原文共 43 页,剩余内容已隐藏,支付完成后下载完整资料

STM32F101xx, STM32F102xx和STM32F103xx单片机的低功耗模式的应用操作说明

介绍

本文是对于软件或者硬件系统设计人员来实现STM32F101xx, STM32F102xx和STM32F103xx产品操作的。它描述了如何使用STM32F10xxx系列产品,详细说明了时钟系统,寄存器设置和低功耗管理方面以满足STM32F10xxx系列产品在低功耗模式的使用。

本文与STM32F10xxx产品和STM32F10xxx参考手册等相关数据表一起阅读。相关信息的编程,擦除和内存保护请参考STM32F10xxx Flash编程手册。

STM32F10xxx数据表和Flash编程手册都是可从STMicroelectronics的网站www.st.com获取。

有关Cortextrade;-M3内核的信息,请参阅《Cortextrade;-M3技术参考手册》,也可从www.arm.com网站获取,地址如下:

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/。

本文的前四部分介绍了STM32F10xxx在低功耗配置的一部分

下一节说明低功耗特性的适用方式。 每个部分都是指与此交付的给出了功率优化的实用视图的软件文件

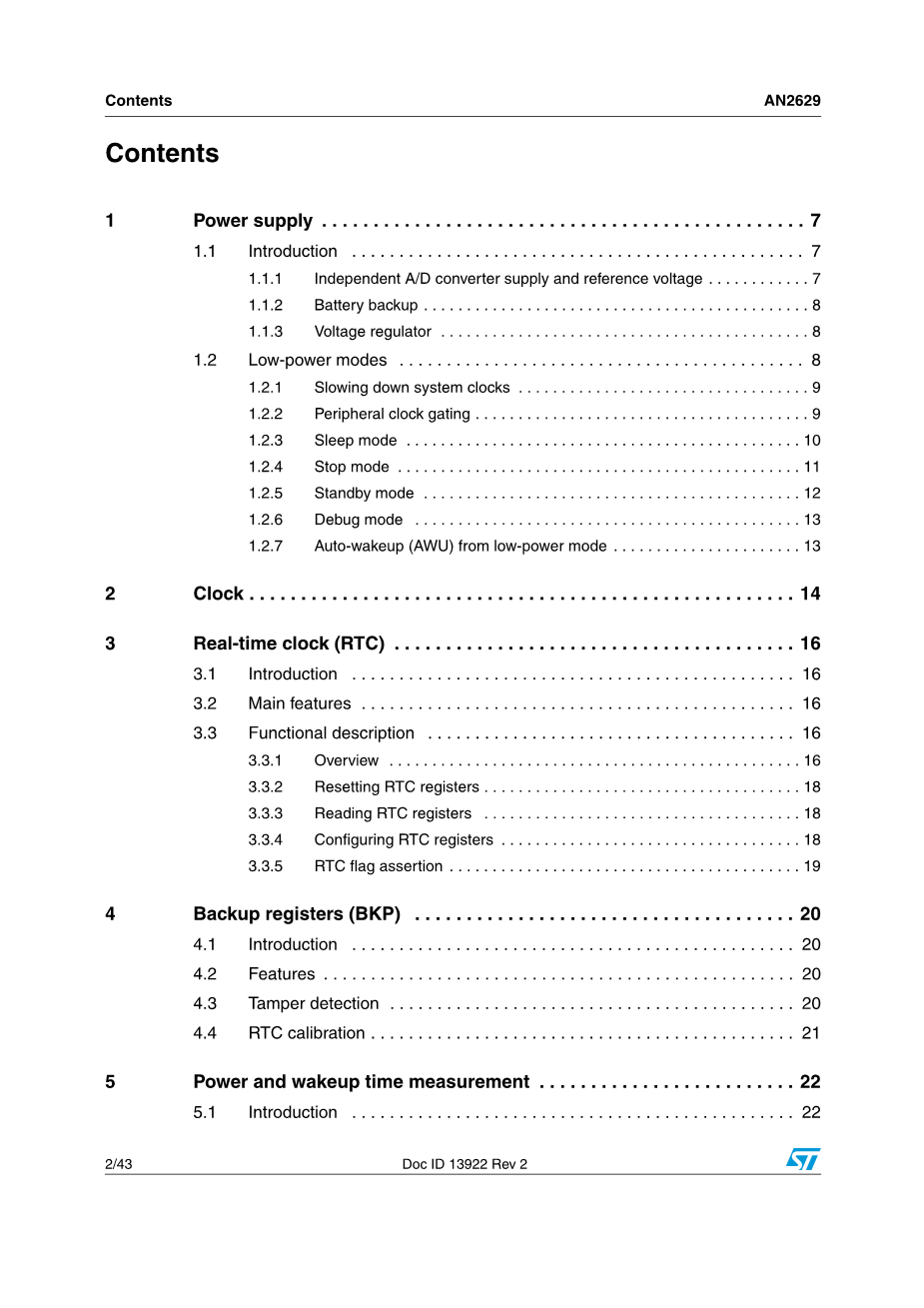

目录

第1章 电源

1.1 简介

STM32的工作电压(VDD)为2.0~3.6V。通过内置的电压调节器提供所需的1.8V电源。

当主电源VDD掉电后,通过VBAT脚为实时时钟(RTC)和备份寄存器提供电源。

电源框图:

1.1.1 独立的A/D转换器供电和参考电压

为了提高转换的精确度, ADC使用一个独立的电源供电,过滤和屏蔽来自印刷电路板上的毛刺干扰。

● ADC的电源引脚为VDDA

● 独立的电源地VSSA

如果有VREF-引脚(根据封装而定),它必须连接到VSSA。

100脚和144脚封装:

为了确保输入为低压时获得更好精度,用户可以连接一个独立的外部参考电压ADC到VREF 和VREF-脚上。在VREF 的电压范围为2.4V~VDDA。

64脚或更少封装:

没有VREF 和VREF-引脚,他们在芯片内部与ADC的电源(VDDA)和地(VSSA)相联。

1.1.2电池备份区域

使用电池或其他电源连接到VBAT脚上,当VDD断电时,可以保存备份寄存器的内容和维持RTC的功能。

VBAT脚也为RTC、 LSE振荡器和PC13至PC15供电,这保证当主要电源被切断时RTC能继续工作。切换到VBAT供电由复位模块中的掉电复位功能控制。

如果应用中没有使用外部电池, VBAT必须连接到VDD引脚上。

1.1.3电压调节器

复位后调节器总是使能的。根据应用方式它以3种不同的模式工作。

● 运转模式:调节器以正常功耗模式提供1.8V电源(内核,内存和外设)。

● 停止模式:调节器以低功耗模式提供1.8V电源,以保存寄存器和SRAM的内容。

● 待机模式:调节器停止供电。除了备用电路和备份域外,寄存器和SRAM的内容全部丢失。

1.2 低功耗模式

在系统或电源复位以后,微控制器处于运行状态。运行状态下的HCLK为CPU提供时钟,内核执行程序代码。当CPU不需继续运行时,可以利用多个低功耗模式来节省功耗,例如等待某个外部事件时。用户需要根据最低电源消耗,最快速启动时间和可用的唤醒源等条件,选定一个最佳的低功耗模式。

STM32F10xxx有三中低功耗模式:

● 睡眠模式(Cortextrade;-M3内核停止,外设仍在运行)

● 停止模式(所有的时钟都以停止)

● 待机模式(1.8V电源关闭)

此外,在运行模式下,可以通过以下方式中的一种降低功耗:

● 降低系统时钟

● 关闭APB和AHB总线上未被使用的外设的时钟。

STM32F10xxx 的低功耗模式图

1.2.1 降低系统时钟

在运行模式下,通过对预分频寄存器进行编程,可以降低任意一个系统时钟(SYSCLK、HCLK、 PCLK1、 PCLK2)的速度。进入睡眠模式前,也可以利用预分频器来降低外设的时钟。

1.2.2 外部时钟的控制

在运行模式下,任何时候都可以通过停止为外设和内存提供时钟(HCLK和PCLKx)来减少功耗。

为了在睡眠模式下更多地减少功耗,可在执行WFI或WFE指令前关闭所有外设的时钟。

通 过 设 置 AHB 外 设 时 钟 使 能 寄 存 器 (RCC_AHBENR) 、 APB1 外 设 的 时 钟 使 能 寄 存 器(RCC_APB1ENR)和APB1外设的时钟使能寄存器(RCC_APB2ENR)来开关外设部时钟。

1.2.3 睡眠模式

进入睡眠模式

通过执行WFI或WFE指令进入睡眠状态。根据Cortextrade;-M3系统控制寄存器中的SLEEPONEXIT位的值,有两种选项可用于选择睡眠模式进入机制:

● SLEEP-NOW:如果SLEEPONEXIT位被清除,当WRI或WFE被执行时,微控制器立即进入睡眠模式。

● SLEEP-ON-EXIT:如果SLEEPONEXIT位被置位,系统从最低优先级的中断处理程序中退出时,微控制器就立即进入睡眠模式。

关于如何进入睡眠模式,更多的细节参考表2和表3。

退出睡眠模式

如果执行WFI指令进入睡眠模式,任意一个被嵌套向量中断控制器响应的外设中断都能将系统从睡眠模式唤醒。

如果执行WFE指令进入睡眠模式,则一旦发生唤醒事件时,微处理器都将从睡眠模式退出。唤醒事件可以通过下述方式产生:

● 在外设控制寄存器中使能一个中断,而不是在NVIC(嵌套向量中断控制器)中使能,并且在Cortex-M3系统控制寄存器中使能SEVONPEND位。当MCU从WFE中唤醒后,外设的中断挂起位和外设的NVIC中断通道挂起位(在NVIC中断清除挂起寄存器中)必须被清除。

● 配置一个外部或内部的EXIT线为事件模式。当MCU从WFE中唤醒后,因为与事件线对应的挂起位未被设置,不必清除外设的中断挂起位或外设的NVIC中断通道挂起位。该模式唤醒所需的时间最短,因为没有时间损失在中断的进入或退出上。

关于如何退出睡眠模式,更多的细节参考表2和表3。

1.2.4停止模式

停止模式是在Cortextrade;-M3的深睡眠模式基础上结合了外设的时钟控制机制,在停止模式下电压调节器可运行在正常或低功耗模式。此时在1.8V供电区域的的所有时钟都被停止, PLL、 HSI和HSE RC振荡器的功能被禁止, SRAM和寄存器内容被保留下来。

进入停止模式

关于如何进入停止模式,详见表4。

在停止模式下,通过设置电源控制寄存器(PWR_CR)的LPDS位使内部调节器进入低功耗模式,

能够降低更多的功耗。

如果正在进行闪存编程,直到对内存访问完成,系统才进入停止模式。

如果正在进行对APB的访问,直到对APB访问完成,系统才进入停止模式。

可以通过对独立的控制位进行编程,可选择以下功能:

● 独立看门狗(IWDG):可通过写入看门狗的键寄存器或硬件选择来启动IWDG。一旦启动了

独立看门狗,除了系统复位,它不能再被停止。。

● 实时时钟(RTC):通过备用区域控制寄存器(RCC_BDCR)的RTCEN位来设置。

● 内部RC振荡器(LSI RC):通过控制/状态寄存器(RCC_CSR)的LSION位来设置。

● 外部32.768kHz振荡器(LSE):通过备用域控制寄存器(RCC_BDCR)的LSEON位设置。

在停止模式下,如果在进入该模式前ADC和DAC没有被关闭,那么这些外设仍然消耗电流。通

过设置寄存器ADC_CR2的ADON位和寄存器DAC_CR的ENx位为0可关闭这2个外设。

退出停止模式

关于如何退出停止模式,详见下表。

当一个中断或唤醒事件导致退出停止模式时, HSI RC振荡器被选为系统时钟。

当电压调节器处于低功耗模式下,当系统从停止模式退出时,将会有一段额外的启动延时。如果在停止模式期间保持内部调节器开启,则退出启动时间会缩短,但相应的功耗会增加。

表4:

1.2.5 待机模式

待机模式可实现系统的最低功耗。该模式是在Cortex-M3深睡眠模式时关闭电压调节器。整个1.8V供电区域被断电。 PLL、 HSI和HSE振荡器也被断电。 SRAM和寄存器内容丢失。只有备份的寄存器和待机电路维持供电。

进入待机模式

关于如何进入待机模式,详见表5。

可以通过设置独立的控制位,选择以下待机模式的功能:

● 独立看门狗(IWDG):可通过写入看门狗的键寄存器或硬件选择来启动IWDG。一旦启动了

独立看门狗,除了系统复位,它不能再被停止。详见16.3节。

● 实时时钟(RTC):通过备用区域控制寄存器(RCC_BDCR)的RTCEN位来设置。

● 内部RC振荡器(LSI RC):通过控制/状态寄存器(RCC_CSR)的LSION位来设置。

● 外部32.768kHz振荡器(LSE):通过备

全文共8799字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[145926],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。