英语原文共 6 页

多通道相位相干射频测量系统

架构和性能考虑因素

David Hall, Andy Hinde, and Yupeng Jia

Systems Engineering America – RF amp; Communications, National Instruments, Austin, TX, USA

摘要 - 无线通信的范例正在转向多输入多输出(MIMO)通信,由发射机和接收机的多个天线实现。 MIMO测试的仪器同步要求是测试行业中最难的一项。在MIMO测试系统中,多通道RF仪器的每个通道必须实现真正的通道到通道相位一致性。虽然MIMO测试设置传统上使用具有共享10 MHz参考时钟的多个VSA,但新的模块化RF仪器允许在多通道VSA的每个通道之间共享单个LO。对于这两种架构,通道到通道相位不确定性的关键因素是不相关的相位噪声和ADC量化噪声。正如这些实验的结果所示,不相关的相噪声主导多通道VSA中的通道到通道相位偏移,其对每个下变频器使用独立的LO。相比之下,ADC量化噪声主导了多通道VSA中的通道到通道相位不确定性,使用每个通道的公共合成LO。此外,在多通道VSA中,绝对通道到通道的相位不确定性明显更好,后者使用每个下变频器链的公共LO。

关键词 - 同步;多通道采集;射频;矢量信号分析仪;矢量信号接收器。

一.介绍

对无线数据的迫切需求促使研究人员寻找新的技术来扩大无线数据和网络容量。如今,许多无线通信系统都采用了多输入多输出(MIMO)天线方案。MIMO依靠多路径来提高无线数据链路的可靠性和有效数据速率,使用多个流,通常通过几个单独的天线。多径传播是对鲁棒通信系统的一个巨大挑战,实际上是通过多种技术(包括空时编码和/或空间分集)利用MIMO来实现的。4G蜂窝标准LTE高级指定在MIMO配置中最多使用八个天线。IEEE802.11n/AC标准和这些标准的实际商业化是MIMO在实践中的主要使用案例。此外,今天的许多现代雷达系统使用电磁波束控制来代替传统的机械控制发射信号。这些应用和其他应用是多通道相位相干射频测量系统需求背后的一些主要驱动因素。

下面的讨论将首先研究什么构成多通道相位相干RF测量系统,然后讨论VSA架构以及它们如何与相位相干系统要求相关。 接下来,将讨论同步多个RF采集通道的方法,以及用于将多个通道的相位对准共同参考的建议技术。其中包括对高级校准注意事项和技术的概述,以及一些测量指标的建议,可用于量化系统一致性性能。 最后,我们将详细分析两种常见同步技术的相位一致性。

二. 相位相关定义和度量

用于测量相位相干性的一种方法是对相同信号进行采样并对所获取的信号相位数据执行统计分析。 利用无源功率分配器分离的CW信号提供多个信号,其相位将彼此相同地移动。 我们可以逐个样本地使用每个通道的相位信息,计算两个RF信号之间的瞬时信道间相位差。 对于每个记录,通道到通道的相位增量是相对于整个记录的平均相位测量的,可以通过以下等式来描述:

在等式1中,Delta;phi;(t),“n”是给定采集中ADC采样的总数,I和Q是每个通道的同相和正交相位采样。 为简化方程式1,我们可以使用该项来表示通道1和2的瞬时相位作为时间3 [1]中时间的函数。

因此,我们用下面的表达式得出给定记录的平均相位phi;的平均值:

从方程2-4,我们可以得到一个简化的表达式来表示双通道相位相干射频采集系统的通道间相位增量:

给出了一种计算通道间相位差Delta;phi;(t)的方法,我们可以通过观察给定一组IQ记录的峰-峰相位差和相位差标准差等特征,定量地评估相位相干系统的性能。

三.基本VSA架构

对射频信号采集多通道间的相位一致性和同步性的讨论必须从研究设备的定时和相位基准开始。

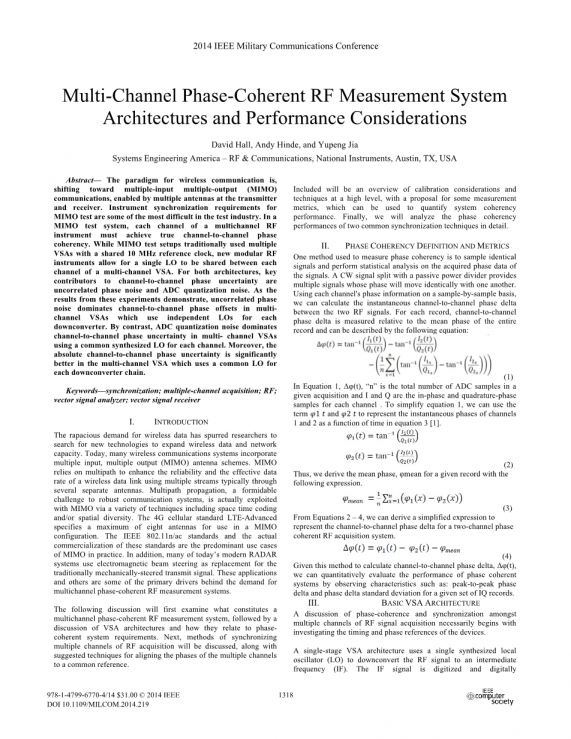

单级VSA结构使用单个合成本振(LO)将射频信号向下转换为中频(IF)。中频信号数字化,数字下转换为基带,产生复杂的I和Q数据样本。在大多数情况下,数字下变频器(DDC)利用数控振荡器(NCO)将数字中频下变频为基带。

图1-简化的单级VSA架构

如图1所示,单级VSA包含多个信号(如黄色所示),可以引入相位不确定性。此外,使用模拟-数字转换器(ADC)从根本上引入了ADC量化噪声,该噪声在每个通道[2]-[3]之间不相关。

四. 多通道同步方法-LOS

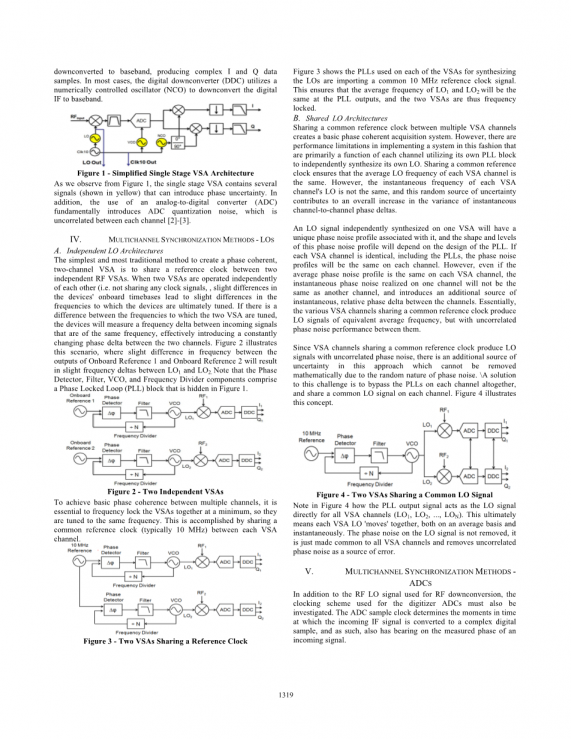

4.1独立的LO架构

创建相位相干双通道VSA的最简单和最传统的方法是在两个独立的RF VSA之间共享参考时钟。 当两个VSA彼此独立操作时(即不共享任何时钟信号,设备的板载时基上的细微差别会导致设备最终调谐的频率略有不同。如果两个VSA的频率之间存在差异。 两个VSA调谐后,器件将测量相同频率的输入信号之间的频率差,有效地引入两个通道之间不断变化的相位差。图2说明了这种情况,输出之间的频率略有差异 板载参考1和板载参考2将导致LO1和LO2之间的微小频率增量。请注意,相位检测器,滤波器,VCO和分频器组件包含一个隐藏在图1中的锁相环(PLL)模块。

图2 - 两个独立的VSA

为了实现多个通道之间的基本相位一致性,必须将VSA频率锁定在一起至少,因此它们被调谐到相同的频率。 这是通过在每个VSA信道之间共享公共参考时钟(通常为10MHz)来实现的。

图3 - 两个共享参考时钟的VSA

图3显示了用于合成LO的每个VSA上使用的PLL正在导入公共10 MHz参考时钟信号。 这确保了PLL输出的LO1和LO2的平均频率相同,因此两个VSA被频率锁定。

4.2共享LO架构

在多个VSA通道之间共享公共参考时钟创建了基本相位相干采集系统。 然而,以这种方式实现系统存在性能限制,主要是利用其自己的PLL块来独立地合成其自己的LO的每个信道的功能。 共享公共参考时钟可确保每个VSA通道的平均LO频率相同。 然而,每个VSA信道的LO的瞬时频率是不相同的,并且这种随机的不确定性源有助于瞬时信道 - 信道相位增量的方差的总体增加。

在一个VSA上独立合成的LO信号将具有与其相关的独特相位噪声分布,并且该相位噪声分布的形状和电平将取决于PLL的设计。 如果每个VSA通道相同(包括PLL),则每个通道的相位噪声曲线将相同。 然而,即使每个VSA信道上的平均相位噪声分布相同,在一个信道上实现的瞬时相位噪声也不会与另一个信道相同,并且引入了信道之间的瞬时相对相位差的附加源。 本质上,共享参考时钟的各种VSA信道产生等效平均频率的LO信号,但它们之间具有不相关的相位噪声性能。

由于共享公共参考时钟的VSA信道产生具有不相关相位噪声的LO信号,因此该方法存在另外的不确定性来源,由于相位噪声的随机性质而无法在数学上去除。 解决这一挑战的方法是完全绕过每个通道上的PLL,并在每个通道上共享一个公共LO信号。 图4说明了这个概念。

图4 - 两个共享公共LO信号的VSA

请注意,图4中PLL输出信号如何直接作为所有VSA通道(LO1,LO2,...,LON)的LO信号。 这最终意味着每个VSA LO在平均和瞬间一起“移动”。 LO信号上的相位噪声不会被消除,它只是对所有VSA通道都是通用的,并消除了不相关的相位噪声作为误差源。

五. 多通道同步方法 – ADCS

除了用于RF下变频的RF LO信号之外,还必须研究用于数字转换器ADC的时钟方案。 ADC采样时钟确定输入IF信号转换为复杂数字采样的时刻,因此也与输入信号的测量相位有关。

对于ADC采样时钟信号,类似于先前关于独立合成的LO与共享LO架构的分析也是如此。 当各个VSA通道之间没有共用的公共参考时钟时,通道之间的时基差异也会导致ADC采样时钟频率略有差异。 采样时钟频率的差异将导致相对采样时钟边沿关系总是在变化,并且与LO信号一样,通道之间缺少频率锁定将阻止相位相干测量。

在VSA之间共享公共参考时钟实现了频率锁定并提供基本的相位一致性,因为ADC采样时钟将以共同的平均频率工作,并且相对采样时钟边沿将保持恒定的平均相位关系。由于采样时钟上存在独特的相位噪声(时钟抖动),在不相关的通道之间仍会存在与此平均ADC采样时钟频率的瞬时偏差。简单共享参考时钟方法的另一个缺点是不能保证合成ADC采样时钟的边沿将在PLL输出处对齐。尽管每个VSA通道将共享公共参考时钟以合成具有共同平均频率的其自己的ADC采样时钟,但是它们的相对平均相位关系通常是不可预测的。一个VSA通道的ADC采样时钟与另一个VSA通道的相位相差180度,而第三个VSA通道的ADC采样时钟与上述参考VSA通道之间可能还有另一个相位增量。这种方法会导致VSA采样时钟边沿之间出现不可预测的偏差,除非采取措施对齐生成的ADC采样时钟边沿,否则不建议这样做。

在所有VSA通道之间共享公共ADC采样时钟信号可消除作为测量系统误差源的不相关相位噪声(抖动),但在物理实现方面引入了一些额外的细微差别。此外,由通道之间的相对ADC采样时钟抖动引入的相对相位测量不确定性远小于由各种VSA LO信号上存在的不相关相位噪声引入的不确定性。以下讨论将显示相对ADC采样时钟抖动误差可以被忽略,有利于更方便的参考时钟共享方法,用于合成单个ADC采样时钟,对相位相干性能的影响可忽略不计,前提是用于对齐ADC样本的机制时钟边缘已实现。

5.1共享采样时钟 - 菊花链拓扑

菊花链拓扑当在多个通道之间共享公共ADC采样时钟时,必须解决时钟共享的物理实现中的其他细微差别。

一个ADC采样时钟共享拓扑涉及将采样时钟从一个VSA通道以菊花链形式连接到下一个VSA通道。 一些VSA提供导入外部ADC采样时钟的能力,这是实现涉及共享的公共ADC采样时钟的方案的最低要求。 此外,一些VSA还能够输出ADC采样时钟,通常通过放大缓冲时钟信号以抵消插入损耗,并保持从一个通道到下一个通道的一致信号电平。 具有导入和导出ADC采样时钟功能的VSA可以实现菊花链时钟共享拓扑,可以轻松添加额外的VSA通道。

菊花链式共享ADC采样时钟实现的缺点是不同VSA通道之间引入的偏差。通过将VSA以菊花链方式连接在一起的电缆将会有一些ADC时钟信号的传播延迟,因此链中第一个VSA接收的ADC采样时钟边沿将比最后一个接收到的ADC采样时钟边沿更早。链中的VSA还有由VSA上的时钟输入/输出信号路径中使用的任何缓冲放大器引入的群延迟,并且以菊花链形式连接ADC时钟信号的外部电缆受到环境热变化的影响,这可能导致相对的变化。这些电缆的长度,随时间改变通道之间的相对偏斜,从而改变相对通道到通道的平均相位关系。最后,应该注意的是,在从一个通道到下一个通道存在复合偏斜的意义上,偏斜是附加的,因此例如将更多通道添加到相位相干VSA系统,第一个和最后一个通道ADC之间的偏斜采样时钟信号将继续增加。

任何上述误差源将影响系统相位一致性的程度将取决于ADC采样时钟频率,下变频器输出的IF频率,时钟输入/输出电路中存在的任何缓冲放大器的特性。 ,用于外部菊花链ADC时钟信号的电缆长度,以及周围环境的温度稳定性。各种VSA通道之间ADC采样时钟偏差的存在意味着VSA不会同时对其输入进行采样, 增加了各种通道相对于彼此的相位相干性的不确定性。 这个问题的程度必然取决于所涉及的应用,但对于需要高度相位相干性的应用,例如相控阵雷达,这种偏斜可能是不可接受的误差源。

同样的现象也适用于菊花链,共享LO拓扑中的LO信号,但是沿着LO共享电缆的传播延迟从一个信道到下一个信道的相移转换为一个VSA与另一个VSA之间的IF信号的相对相移。。 将进一步讨论校准,但是该LO相移简单地转换为整个特定VSA通道的相移,并且可以在通常已经执行的简单对准校准中考虑。 然而,ADC采样时钟的偏斜导致在稍微不同的时刻获取数据,并且在某些情况下即使不是不可能也难以在事后考虑。

5.2共享采样时钟 - 星形拓扑

面对由菊花链时钟共享拓扑引入的ADC采样时钟偏差的缺点,一种解决方案是使用单独的器件合成ADC采样时钟,并使用外部零度功率分配器为多个VSA创建多个信号 ADC采样时钟输入。 相位匹配电缆可用于将功率分配器输出连接到VSA ADC采样时钟输入,表面上现在可以消除ADC采样时钟偏移,因为从功率分配器输出到ADC采样时钟输入的每条路径现在都相同的电气长度。

星形拓扑方法的明显缺点是需要单独的外部时钟源来提供主ADC采样时钟信号。 这提高了相位相干系统的成本,并且可能也增加了系统的占地面积。 此外,ADC采样时钟分离器损耗随VSA通道数量而变化。 例如,双通道VSA系统需要一个双向,零度功率分配器,其分路器损耗为3 dBFour VSA通道需要一个四路零度功率分配器,分路器损耗为6 D b。 8路功率分配器具有9 dB的分配器损耗,并且损耗随分频器输出的数量而变化,因此具有显着通道数的相位相干系统可以非常快速地实现从该扇出中足够的ADC采样时钟损耗,从而需要ADC之间的放大器 采样时钟源和功率分配器,增加了成本和复杂性。

虽然星形拓扑表面上消除了ADC采样时钟偏差作为相位相干系统中的不确定性来源,并且肯定导致比菊花链式ADC采样时钟共享拓扑更小的相对偏移量,但是星形拓扑结构并未消除ADC样本时钟完全歪斜。零度功率分配器并不理想,并且不会导致每个输出完全同相,在功率分配器规范文档中称为相位跟踪的性能度量。用于将功率分配器输出连接到VSA ADC采样时钟输入的相位匹配电缆将不是完全相同的电气长度,尽管它们将接近并且由电缆制造商提供的公差指定。最后,电缆将位于VSA的外部并受到环境热变化的影响,这些变化的温度梯度导致电缆长度的膨胀/收缩略有不同,导致ADC采样时钟传播延迟通过路径发生轻微变化。

5.3国家仪器触发时钟技术-

资料编号:[6015]

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。