英语原文共 10 页,剩余内容已隐藏,支付完成后下载完整资料

用于高速低抖动宽范围占空比校正器高精度ADC

Minjie Liu, Yingzi Jiang, Siwan Dong, Zhangming Zhu n , Yintang Yang

微电子学院,西安电子科技大学,西安710071,中国

文章信息 :

文章历史:

初稿2014年6月11日

修改稿 2015年1月28日

2015年2月17日通过

2015 年3 月11 日上传

关键字: 电荷泵;A / D转换器;占空比校正器;时钟抖动

摘要

本文提出了一种用于高速,高精度流水线A / D的占空比校正器(DCC)电路转换器。组合电荷泵用于确保电流源和电流的稳定性吸收,可以抑制电荷共享效应,从而提高了占空比的精度输出时钟。为米勒的差分输出增加了具有米勒电容的二阶低通滤波器组合式电荷泵不仅节省了面积,而且还提高了环路稳定性,从而扩大了输入占空比范围(10–90%)。该电路还可以有效抑制时钟抖动。后仿真结果基于SMIC 65 nm CMOS工艺。输出时钟的占空比精度建议的DCC中的信号为5070.2%。在200 MHz输入频率下,27 1C TT处理角,RMS抖动约为186.6 fs,峰峰值抖动约为1.447 ps。使用2.5 V电源电压时,功耗功率为1.88 mW,有效芯片面积为0.02 mm2。这项工作已成功应用于13位200MSPS A / D转换器。

2015 Elsevier Ltd.保留所有权利。

1.介绍

对于A/d转换器,其分辨率为8-16个比特和所述采样频率从兆字节到几百兆字节,流水线A/D转换器是一种主流的实现结构[1]。在典型的流水线A/D转换器中,输入时钟的两个边沿必须用于产生电路所需的各种定时信号核心。对于上升边沿的所述时钟被用于采样输入信号和孔定量网络连接的偶数段的阳离子的管道,和的下降沿的时钟用于保持所述输入信号和所述孔定量网络的阳离子的管道的奇数阶段,时钟占空比必须精确地保持在50%。另外,在高频率输入信号,冲击的时钟抖动的转换整个系统的准确性和SNR性能将变得越来越大。时钟源由外部产生水晶,但其职责周期的稳定性和精度都无法满足的的要求的整体A/d转换器[2]。因此有必要设计一个专门的时钟占空比周期中校正芯片。

锁相环(PLL)或延迟锁定环(DLL)能够被用于实现时钟占空比校正器。常规PLL电路和DLL电路仅能够锁定的频率和输入和输出信号的相位,但占空比不能实现设定的目标。正如前面提到的,工作周期所述的时钟信号是一个重要的性能参数,以A/d转换器,那么,基于DLL原理的DCC电路可以用于调制输出信号占空比。在理想之下在这种情况下,DCC电路可以传输任何占空比的输入信号周期分成一个50%占空的输出信号周期[3]。

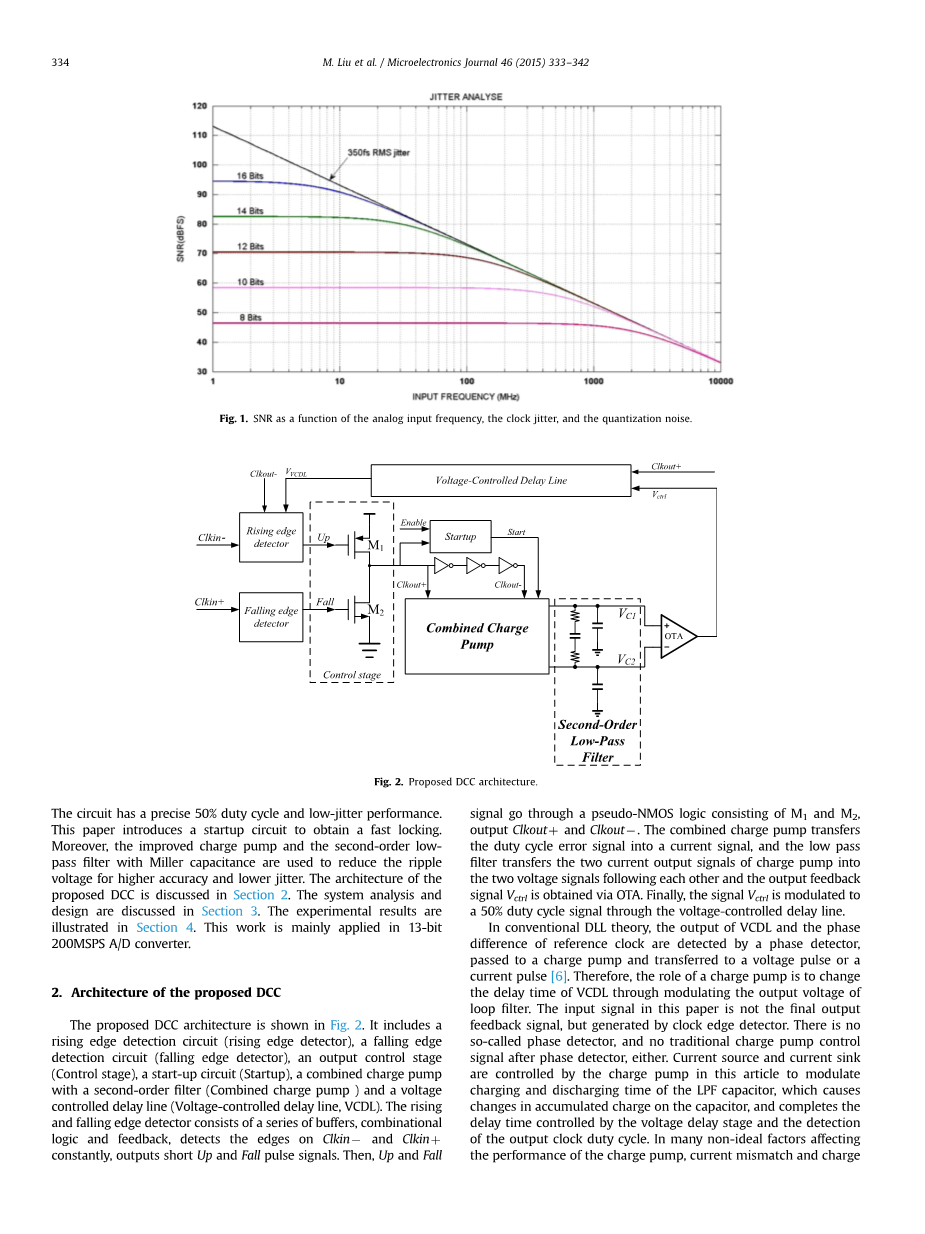

A/d转换器需要采样模拟数据,所以在时钟信号性能对于整个系统很重要[4]。如图在图1,SNR是模拟输入频率,时钟抖动的函数和量化噪声。时钟抖动是位置变化时钟沿,这将导致采样错误,直接导致精度的整体输出错误的的ADC。随着增加输入频率,时钟抖动引起的转换误差将增加。增加模拟输入频率将增加的斜率的输入信号,其放大倍数音响ES中的转换错误。这是请务必注意,转换误差的幅度为相对-一个0.5LSB(最显网络连接着的位)转换为错误一个10位device等效于16位设备的32LSB错误。这个这意味着时钟抖动变得越来越重要,因为两个ADC分辨率和模拟输入频率提高[5]。

(1)

其中 在是模拟输入频率的满量程正弦波,是时钟抖动的rms值,是平均的所述差分非线性, 是ADC的有效输入噪声,并且N 是所述ADC有效位数。

在要求旨在用于时钟高速的信号和高精度A / D转换器,本文提出了一种新颖的DCC 电路

与组合的电荷泵结构和二阶网络滤波器。

图1. SNR 作为模拟输入频率,时钟抖动和量化噪声的函数

该电路具有一个精确的50%占空周期和低抖动性能。 本文介绍了一种用于快速锁定的启动电路。此外,改进的电荷泵和低阶二阶 通连接用米勒电容滤波器被用于减少纹波更高的精度和更低的抖动电压。的结构的建议的DCC将在第2节中讨论。系统分析与设计将在第3节中讨论。实验结果在第4节中进行了说明。这项工作主要适用于13位200MSPS A / D 转换器。

2.提议的DCC的体系结构

提出的DCC体系结构如图2所示。它包括一个上升沿检测电路(上升沿检测器),下降沿检测电路(下降沿检测器),输出控制级(控制级),启动电路(Startup),组合电荷泵与第二阶连接的滤波器(联合电荷泵)和电压控制的延迟线(压控延迟线,VCDL)。该上升和下降沿边缘检测器包括的一个系列的缓冲器,组合逻辑和反馈,检测在边缘Clkin-和Clkin 持续输出短路的上升和下降脉冲信号。然后,上升和下降信号经过由M 和M 组成的伪NMOS逻辑,输出CLKOUTthorn;和CLKOUT阑。组合电荷泵传输占空周期误差信号转换为电流信号,并且将低通音响滤波器两个电流传送电荷泵的输出信号进两个电压以下信号的每个其它和输出反馈信号VCTRL被经由OTA获得。最后,信号Vctrl被调制为50%的工作循环通过信号压控延迟线。

图2. 建议的DCC 体系结构

在传统的DLL的理论,VCDL和的输出的相位参考时钟的差异由相位检测器检测,传递给电荷泵,并转移到一个电压脉冲或一个电流脉冲[6]。因此,该角色的电荷泵是变化通过调制VCDL的输出电压来延长VCDL的延迟时间循环网络滤波器。本文中的输入信号不是网络连接最终输出反馈信号,但由时钟沿检测器产生。有没有所谓的鉴相器,没有传统的电荷泵控制相位检测器后的信号。电流源和电流吸收器在本文中由电荷泵控制以进行调制LPF电容器的充电和放电时间,这会导致改变积累的电荷上的电容,并完成了延迟时间由电压延迟级和检测控制所述的输出时钟占空比周期。在许多非理想因素中影响电荷泵的性能,电流失配和电荷共享效应是充电时,特别重要的解散充电[7] 。因此,添加了启动电路以设置初始值电荷泵的状态;使用组合的电荷泵浦是改善的效果不理想因素带来的,和一个二阶低通网络滤波器是在最后添加到降低电压FL 波动由于充电和放电的电荷的泵。时序图的的提议DCC示于图3 。的输入信号Clkin 不是50%占空比。通过边缘检测下降沿处理检测器,该下降缘被接通到所述 下降脉冲信号。然后,秋季脉冲信号触发的晶体管M1 ,产生输出信号Clkout 的下降沿并保持低。之后,通过VCDL 的延迟和反馈朝向输出信号Clkout 的下降沿,即上升脉冲信号产生触发的晶体管M1 和使所述1个上升沿的所述输出信号CLKOUT 。经过不断的反馈整体反馈环路的调整,工作周期中的输出信号将达到精确的50%,即环路最终达到稳定。

图3. 时序图的所提出的DCC

3.时钟边沿检测器

下图4是上升沿检测器和下降沿探测器。与常规时钟发生器或相位相比检测器,其总是检测输入时钟信号,该建议上升沿检测器被用于检测的边缘,这是在在电压控制延迟线上输出电压信号。的提出下落边缘探测器检测的正输入时钟信号并通过一系列产生具有一定宽度的脉冲信号Up逻辑电路,上升沿检测器类似地产生下降。

图4. 时钟边沿检测器

上升沿检测器的时序图如图所示。图5(a)。当时的低级别的输出电压的电压-控制延迟线被变成高电平。由于该上升沿检测器检测该变化的边缘的所述输出信号,窄脉冲信号Up被触发并输出信号,窄脉冲信号Up被触发并输出信号Clkout 是在低电平。之前被打开,信号V具有被保持在高水平。因此,通过“与非”门,和产生低电平窄信号Up。信号Up控制晶体管M1,所以所述的逻辑状态的输出时钟信号的变化从低到高。之后的一些延迟时间数反相器,信号变为低电平,使信号Up弹回到高电平。然后上升沿检测器达到电压信号的边沿检测并产生一个低电平电平窄脉冲具有六个门脉冲宽度的延迟时间。

下降沿检测器的时序图显示在图5(b)。当所述输入信号Clkin 从低电平弹到高电平,信号从高电平弹到低电平。虽然之间的信号和V,存在由产生的延迟时间的逆变器。在该该信号的时刻VFLIP,该信号V仍保持低。2sip从高级别到低级别。同样因此,NAND门意愿输出一个高电平脉冲信号Fall,和输出信号的逻辑状态Clkout 被改变通过伪NMOS逻辑功能。正如提到的之前,Clkout 被变成Clkout-后的延迟的3反相。当信号的逻辑状态Clkout-变化,所述晶体管M到信号VFL的ip到高电平,这使得信号V48伪逆变器逻辑中包含的是由于关闭弹到高3电平和信号Fall弹回低的水平,并保持在信号Clkout 在低电平,直到时钟上升沿来。

图5. 时序图的上升边缘检测器和下降边缘检测器

4.启动电路

本文基于D的触发器启动电路原理如下:当DCC 开始工作,将启动电路输出有一定宽度信号启动具有高窄脉冲,它将节点电压到M放电。当该放电完成的初始输出电压的电荷泵使延迟的输出时钟信号具有最大脉冲宽度。在下一个调试过程中,电荷泵电荷的节点电压为,这增加了延迟的VCDL输出边沿的到达,直到电路锁定到目标占空比。

如图6 所示,本文的启动电路工作原理如下:当使能信号为零时,在几个周期内 输入时钟信号在整个电路不启动工作,输出时钟信号Clkout是在低电平,并且输入时钟相对信号是Clkin ; 在该时刻,时钟脉冲Clkin 变低,节点A被连接通过传输门连接到VDD,并用节点B计算这也在高级别通过NAND 门。然后所述节点C是转向高点的上升边Clkin 。在该同一时间的 节点C 和D去通过NAND 门和输出低电平节点E,经由逆变器1。该高层脉冲启动使电荷泵V C 1 的输出节点放电,时钟输出信号Clkout 的上拉完成。通过NAND门,启动变为低电平,并保持低电平的所有时间。

图6. 启动电路

5. 组合电荷泵回路

如图7 所示,建议的组合电荷泵 检测占空比输出电流信号,以及LPF 将该电流信号转换成电压信号 和 。如输入的一个单级的跨导放大器,个输出控制电压。使用相同大小的,,,,偏置晶体管使漏极电压的电荷泵电流源和电流槽等于所述漏极电压的所述 偏压晶体管,所以该充电和放电电力损失 避免了由信道调制效应引起的。偏见的电压的电荷泵电流宿和电流源使用自偏技术。虽然四个开关的电荷泵将关闭,节点A和B的纹波电压为通过使,,,的漏极电压恒定来避免当两个开关闭合时电荷共享效果被抑制。在这个DCC电路中,纹波的大小输出控制电压将直接影响在输出时钟的占空比和抖动的时钟边缘的精度,并且所述电荷泵电路的性能直接影响。

电荷共享效应可能也导致该节点电压波动,从而其影响时钟信号的精度。在组合电荷泵的基础上跟随电路中加入两个平行分支是为了抑制节点电压波动。从动电路包括5个MOS晶体管 和 。它包括作为输入和的晶体管,以二极管的连接形式连接到提高M8的漏极电位。和大小相同,所以有

(2)

(3)

所以有=, 然后产生电压钳位。当开关关闭,节点X和Y电压的波动为避免了,抑制了电荷共享效应。在偏压电路,放大器的负反馈功能使=。

电荷泵电路的输出电压性能具有对输出时钟抖动性能的重要影响。尽管在理想条件下的电压纹波为不可避免且不会影响输出时钟抖动,纹波电压的增加会引起其他非理想因素,例如电流源和电流的通道长度调制效应下沉,以降低时钟占空比和抖动特性。减少输出电压的波动电荷泵,抖动衰减放大器和低通滤波器加在电路中以使输出幅度电压纹波更低。电路中添加的低通滤波器可以部分消除了高频杂散的影响,但是LPF中的大电容可能会造成面积损失。因此,设计一个和之间的单级跨导放大器抖动衰减放大器可降低输出电压纹波,改善了DCC电路的整体特性,并抑制时钟抖动。通过放大单级跨导,输入电压输出控制电压驱动延迟线以产生不同的延迟时间。

图7. (a)建议的组合电荷泵 (b)建议的追随者和OTA

6. 二阶低通网络滤波器

低通滤波器的功能是转移电荷泵将电流信号输出到电压信号中必须选择LPF的结构来稳定整个DCC系统。本文中的组合电荷泵需要两个对称低通滤波器结构。传统的一阶低通滤波器图8(a)示出了具有米勒电容的电容器。传统DCC电路使用大电容作为LPF来实现具有输入占空比范围非常窄。如图8(b)所示,提出了具有米勒电容的二阶低通滤波器本文为了减少该地区的损失,在其中更大可以提供输入占空比范围。它被添加到两个输出电荷泵的两端并将电流信号传输到电压信号和,它们使和同时完成。根据米勒定理,与非米勒结构相比,该结构的总面积使用Miller电容将减少75%[8]。较小的电容器C1和一阶RC滤波器可以是并联连接形成一个二阶滤波器[9]。当时电荷泵对RC过滤器进行充放电,输出电压会有很大的波动。一个小的电容器C1会增加系统的极点,这会影响系统的稳定性,那么会影响调制范围输入频率和输出时钟抖动。因此,系统稳定性是一个至关重要的问题。

图8. 米勒方案 (a)第一阶米勒方案和(b)第二阶米勒方案

7. 理论分析与仿真

如图9所示,在初始工作时间,节点电压电荷泵通过启动电路排出。输入时钟频率为200兆赫,输入占空比为10%,如图9所示。在启动状态结束,VCDL的控制电压与成反比的是最大值,这使得VCDL产生最小延迟时间并导致输出时钟在启动状态结束时达到峰值。随着

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[237487],资料为PDF文档或Word文档,PDF文档可免费转换为Word