英语原文共 20 页

3、随机故障控制技术

原则上,可以通过检测来管理随机故障,然后进行补偿。

3.1 检测方法

当系统中存在冗余时,最简单的方法是比较两个独立的计算结果、输入、数据等。当功能结果与一些一致性约束进行比较时,有价值的检测方法也可以基于验收测试(例如有效区间、范围或值的组合)。另一种检测方法是将几个相对成分的结果进行比较,或者将结果与特定计算的预期结果进行比较(例如使用正交试验,例如RAM测试)。

当检测是唯一适用的方法时,在检测到危险的错误后,应该停止系统并将其置于故障安全状态,或通过确定的恢复过程,如复位、回滚或另一个特定的检查,如替换受影响的组件(以钝化错误)。异常情况下,如果可以容忍,系统可以继续以某种降级模式运行,或者提供错误/无效的结果,向其环境表明系统已经失败。

3.2 补偿方法

补偿方法通常允许系统继续正常运行。

补偿可以通过纠错或掩蔽来提供。在校正模式下,正确的结果是使用冗余信息(如ECC)从错误的结果中计算出来的。在屏蔽模式下,错误的结果将被忽略,如果可用,将使用冗余资源(下一个通道、输入、输出或数据)。正确的结果可以通过确定投票过程的结果来确定,只识别组件的坏的和正确的部分,或损坏和正确的数据。

标准承认硬容错(HFT -系统在继续正常运行时能够吸收的最大错误数)。

除了特定的功能测试外,冗余是诊断的基本原则。大多数检测和补偿技术都需要一定程度的冗余才能有效。补偿比检测要求高得多,因为不仅要找出差异,而且还要另外确定正确的状态。为此,必须采用具体的比较和投票机制以及逻辑。

4、适用于冗余技术

所需的冗余级别可以通过多种不同的方法和技术来实现。这种技术可以同时使用硬件和软件,或者将它们结合起来,以最大限度地提高效率和诊断覆盖率。当需要补偿时,增加输出比较和正确路径与故障路径之间的特定投票机制是每个冗余系统实现的组成部分。

4.1 结构冗余

结构冗余是基于并行相同(对称)结构执行相同的当代任务。

在系统级,可以使用双寄存器、内存、cpu甚至内置的整个微控制器。在应用层面,一些关键的输入或输出可以翻倍或三倍(包括数字和模拟),可以使用一对协同的微控制器,可以应用双传感器、执行器、通信总线等。

4.2 功能冗余

功能冗余是基于并行的不同(非对称)HW结构或不同的SW方法,应用于一个任务。

例如,CPU行为可以通过特定的内置HW检查器进行监视,或者执行主任务的32位微控制器可以通过外部更简单的8位微控制器进行监视,检查一些交叉结果,或者在比较输入和输出时保护主系统行为的某些特定方面。软件可以通过一些粗略的简化算法,如定点整数计算或一些复杂逻辑决策方案的结果与简化后的结果进行比较,对一些复杂的流点计算结果进行重新计算和复核。

4.3 时间冗余

当同一方法在不同时隙中被同一HW或SW多次应用时,实现了时间冗余。

典型的例子是锁步双核心微控制器,每个核心执行相同的任务,但在不同阶段的核心时钟脉冲。在应用程序级,软件可以连续多次重复相同的计算或逻辑任务,并对结果进行比较。

4.4 信息冗余

当添加的信息在数据上实现并由HW或SW评估符合性时(例如奇偶校验位、ECC、CRC校验模式、数据协议、数据拷贝等的实现),信息冗余是最常见的一种。

5、应用方法

5.1 聚焦于供应商

从安全的角度来看,微控制器是一种复杂的可编程电子元件,必须满足相关标准的特定要求。

当保证微控制器的安全性时,供应商会将该产品视为上下文之外的组件,因为它的最终应用程序和安全任务并不预先知道。始终致力于覆盖组件的总体可靠性,并满足应用程序所针对的给定安全完整性级别的标准所定义的诊断覆盖率的总体预算。

像微控制器这样的复杂组件可以看作是安全任务中涉及的部分组件。每个部件都有自己的诊断覆盖率和重量,从而为整个部件的安全预算做出贡献。

保持所需的总体安全预算的有效方法是将重点放在微控制器的关键和通用模块上,特别是那些贡献最大的模块和大多数应用程序更常用的模块。这些模块上的任何小的安全改进都能给组件的总体安全预算带来最大的收益,因为它具有较大的重量和重要性,从而使所有应用程序受益。

对于软误差,最有效的部分是由SRAM使用,它占据了模具整个区域的重要部分,并被每个应用程序所使用。这就是为什么本应用程序说明特别关注适用于易失性内存的方法。

根据安全标准,软件错误的定义需要可恢复能力。从这个角度来看,我们可以把可编程NVMs中的数据保留失败作为一个例子。在检测到这些故障之后(例如通过ECC内置或软件检查),在软件驱动的正确恢复过程中,可以将正确的模式编程回内存(如果已知)。

除了专注于内存的硬件安全特性(因为它们的重要贡献),STM32微控制器还实现了许多其他支持特性。

表1给出了一个概述。更多的细节可以在专门的参考和安全手册中找到。

5.2 聚焦于用户

一旦用户将微控制器包含到应用程序设计中,并且指定了安全任务,那么安全支持就可以以更有效的方式展开,覆盖所需安全案例中涉及的特定部分。

基于对应用要求、设计、过程和所控制设备的详细了解,可以应用许多有效的方法。冗余和系统行为的知识是关键原则,可以单独应用,也可以以通用的方式应用。输入和输出可以通过反馈循环进行相乘或检查,测试趋势或时间间隔中的逻辑状态、值或预期响应。通信数据可以通过冗余信息甚至加倍来保护。可以监控这些流程的正确时间和流程顺序,以检查正确和完整的控制序列。通过比较来自冗余流和独立流、分析、计算或数据的结果,可以做出正确的决策。

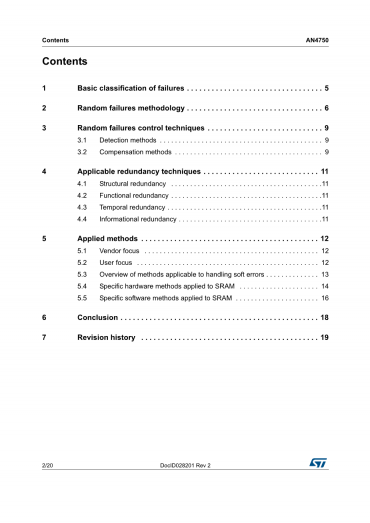

5.3 适用于处理软件错误的方法概述

表1概述了硬件和软件处理STM32微控制器软件错误的直接或间接方法,以及它们与IEC 60355标准要求的关系。概述仅供参考。大多数列出的项目和方法都有一个覆盖层,因为它们直接或间接地符合不同的诊断目的。

表1.适用的方法处理软件错误支持的STM32 HW功能

|

HW特征或SW方法 |

解决目标 |

方法 |

IEC 60355 - B类参考文献 |

|

ARM Cortexreg;核心例外/定期核心自我测试 |

影响核心功能的永久性故障不可预测的软件或系统行为或故障捕获 |

处理系统异常中断,测试使用核心寄存器操作的指令序列 |

IEC 60335 R.1.1 – H.2.16.5 – H.2.16.6 – H.2.19.6 |

|

检查应用程序中断系统 |

预期和意外中断检查 |

检查应用程序中断丢失或太频繁 |

IEC 60335 R.1.2 – H.2.16.5 – H.2.18.10.4 |

|

时钟测量与校验 |

检测错误或缺失的频率,具体的XTAL检查 |

时钟安全系统CSS控制,独立看门狗,内部时钟交叉参考测量 |

IEC 60335 R.1.3 – H.2.18.10.1 – H.2.18.10.4 |

|

闪存/不变内存自测ECC(内置CRC模块支持自测) |

永久故障影响系统闪存单元和地址解码器 |

在DTI中定期执行内存块的ECC或CRC签名计算 |

IEC 60335 R.1.4.1 – H.2.19.3.1 – H.2.19.3.2 – H.2.19.8.2 |

|

在SRAM /变量内存自我测试奇偶校验位 |

永久故障影响系统SRAM内存单元和地址解码器 |

在字节读取或周期性检查时,每8位单词检查一位 在DTI内定期执行人行道测试 |

IEC 60335 R.1.4.2, 1.4.3 – H.2.19.6 – H.2.19.8.2 |

|

控制流监控 独立和窗口看门狗 |

适当的软件定时程序计数器失控或挂起 |

运行时控制应用程序的软件流程和应用程序相关的定时,处理看门狗超时 |

IEC 60335 R.1.6.3 – H.2.18.10.2 – H.2.18.10.4 – H.2.18.18 |

|

双GPIO数字输入或输出,数字输出的环回方案 |

作为数字输入和输出的GPIO线路上的永久和瞬态故障 |

应用程序设计 |

IEC 60335 R.1.7 – H.2.18.13 |

|

模拟输入和输出范围/可信性检查 |

影响ADC和多路复用器的永久性故障 |

应用程序设计 |

IEC 60335 R.1.7.2 – H.2.18.13 |

|

通信加强HW和SW技术,处理协议错误 |

数据处理中的错误 |

协议,双通道,CRC模式,重复消息 |

IEC 60335 R.1.6 – H.2.19.8.1 – H.2.19.4.1 – H.2.18.2.2 – H.2.18.14 |

|

安全关键数据的信息冗余 堆栈淬火技术 |

单片机内部事务冗余,易失性存储器保存安全关键信息 |

安全变量验证 传递参数的合理性 |

IEC 60335 R.1.5 – H.2.19.8.2 |

|

电源监控器(POR, PDR, BOR) 内部温度监测 选项字节保护 SRAM的保护 配置锁定/定期读取配置寄存器(包括未使用的外围设备)(1) |

安全的工作环境,确保系统各部分功能正常 |

中断呼叫紧急关机任务或保持设备处于重置状态,验证所有安全关键系统配置 |

无对应文献 |

(1)减少可能在相同输出插脚(潜在故障)上发生冲突的外设之间的交叉干扰的可能性。

5.4 应用于SRAM的特定硬件方法

其中最有效的方法之一是双柱塞结构与比较器。RAM被分成两个块,所有数据都被镜像。每次读取之前,都会对这两个区域的值进行硬件比较。使用EDC或ECC(错误检测或纠正代码)保护单词的效率稍低。标准情况下,汉明码应用的距离大于3(每个32位的单词中必须添加一定数量的检查位),这至少涉及分段(单个单词内进行一次错误纠正和两次错误检测)。

一些STM32微控制器使用奇偶校验位(每8位一个字)应用于整个或RAM的一部分,这足以识别保护字的单个位或奇数位错误。并不是所有的覆盖多个比特错误,该方法有效的分布式设计时收集的碎片在个字应用(设计多路复用因子物理距离的两列载有两个逻辑上它毗邻-应该保持大于4)。在这种情况下,当代的概率乘以比特错误在一个通量或EMI攻击相对较低。

累积位错误执行另一种情况,当两个单一位错误可以发生在同一个单词中,两个后续攻击出现在不同的时间。这就是为什么建议将硬件奇偶校验与定期擦除SRAM中不经常使用的区域相结合,特别是由软件进行擦除,软件可以通过及时检测单个位错误来防止这种累积错误,示例如图4所示。

除了防止多比特错误外,这种擦除方法还可以在执行安全关键程序之前预先检测SRAM中的潜在错误(然后是潜在的数据差异)。

在Nucleo F030R8板上执行此类测试的简单示例代码与此应用程序说明相关联。此示例的源文件在请求时可用,用户应与本地字段应用程序工程师联系。

该示例使用STM32F0,但是它可以很容易地适应其他在SRAM上具有硬件奇偶性的产品。用户可以简单地将附加文件包含到Cube HAL (EWARM project)的模板目录中。擦洗过程在IAR汇编程序中编写为优化代码(参见stm32f0xx_pchck_IAR文件)。在main.h头文件中,用户可以控制配置。软件可以根据定义的条件编译参数进行检测或添加补偿方法。在补偿的情况下,该算法在RAM工作区清洗过程中对工作数据进行备份。此方法适用于工作区域内的数据不经常更改,因此不能应用于专用于堆栈的区域。当在RAM的工作部件中检测到奇偶校验错误时,将从其备份副本中恢复正确的数据。

奇偶校验错误检测引发硬故障异常。它的处理有点棘手,因为在从处理程序和被测试地址的指针返回之前,必须由特定的包装器恢复正确的返回地址,否则测试流将被中断,无法正确继续。

对于应用LDMIA或LD

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。