英语原文共 6 页,剩余内容已隐藏,支付完成后下载完整资料

译文

功率模块的翘曲分析与改进

摘要:

与单芯片功率模块封装相比,由于内置多个芯片,功率模块通常具有更大的尺寸。这可能在组装过程中引起相当大的封装翘曲,尤其是在模制之后,这使得封装翘曲对DBC衬底以及在应用期间将功率模块安装到外部散热器时的硅芯片上的影响很大。因此,本文研究了功率模块的模塑过程后的翘曲,并介绍了一种改进方法。在模制之后,功率模块的DBC侧可能具有凸出的翘曲。为了减少凸翘曲,在模制过程中产生DBC基板的预凹翘曲,以平衡部分凸翘曲。然而,在传递模塑过程中,DBC侧的凹形轮廓可能在DBC区域周围引起一些闪光问题。对功率模块的封装翘曲进行了FEA建模和实际测量。结果发现,FEA模拟结果的趋势与封装翘曲的测量数据一致。通过平衡翘曲问题和闪光问题,提出了用于大规模生产的DBC基板的预凸翘曲的更好选择。

1.介绍

对高度集成的电子设备的需求正在推动电源封装行业为下一代多芯片系统封装(SiP)开发先进的封装解决方案。陶瓷基板和有机聚合物基板都已成功用作集成半导体芯片的载体,以实现功率模块封装[1-4]。对于高压功率模块,由于具有高载流量、高隔离性能和高导热性的特点,多个模具附接到一个或多个陶瓷基板。电力电子产品用于许多不同应用的消费产品和工业产品,从混合动力和电动汽车的逆变器,风能和太阳能的电力转换,火车的牵引驱动,到医疗共振成像(MRI)放大器[5]。在客户现场应用中,电源模块通常安装在外部散热器上,然后安装到应用PCB板上,以实现更好、更高效的散热。

功率模块通常具有更大的尺寸。由于不同材料的CTE不匹配和塑封料在固化过程中的化学收缩,这可能在模具加工后引起相当大的封装翘曲。在应用过程中,将功率模块安装到外部散热器时,翘曲会对DBC基板产生很大影响。功率模块包括DBC基板,功率管芯和无源元件,引线框架和环氧树脂模塑料。在模制之后,由于不同材料的CTE不匹配和塑封料的化学收缩,功率模块的DBC侧可能具有凸出的翘曲。为了减小凸翘曲,在模制过程中产生DBC基板的预凹翘曲,以平衡部分凸翘曲。然而,在传递模塑过程中,DBC侧的凹形轮廓可能在DBC区域周围引起一些闪光问题。因此,需要优化凹形轮廓以平衡翘曲问题和闪光问题。针对DBC基板预凹翘曲的不同值和模式,设计了几种不同的方法来获得优化的封装翘曲。对功率模块封装翘曲的有限元建模和实际样本评估进行了深入研究。在FEA模拟结果和测量数据之间检查相关性。结果表明,有限元分析仿真结果的趋势与功率模块翘曲的测量数据一致。通过平衡翘曲问题和闪光问题,提出了用于大规模生产的DBC基板的预凹翘曲的更好解决方案。

2、翘曲计算方法

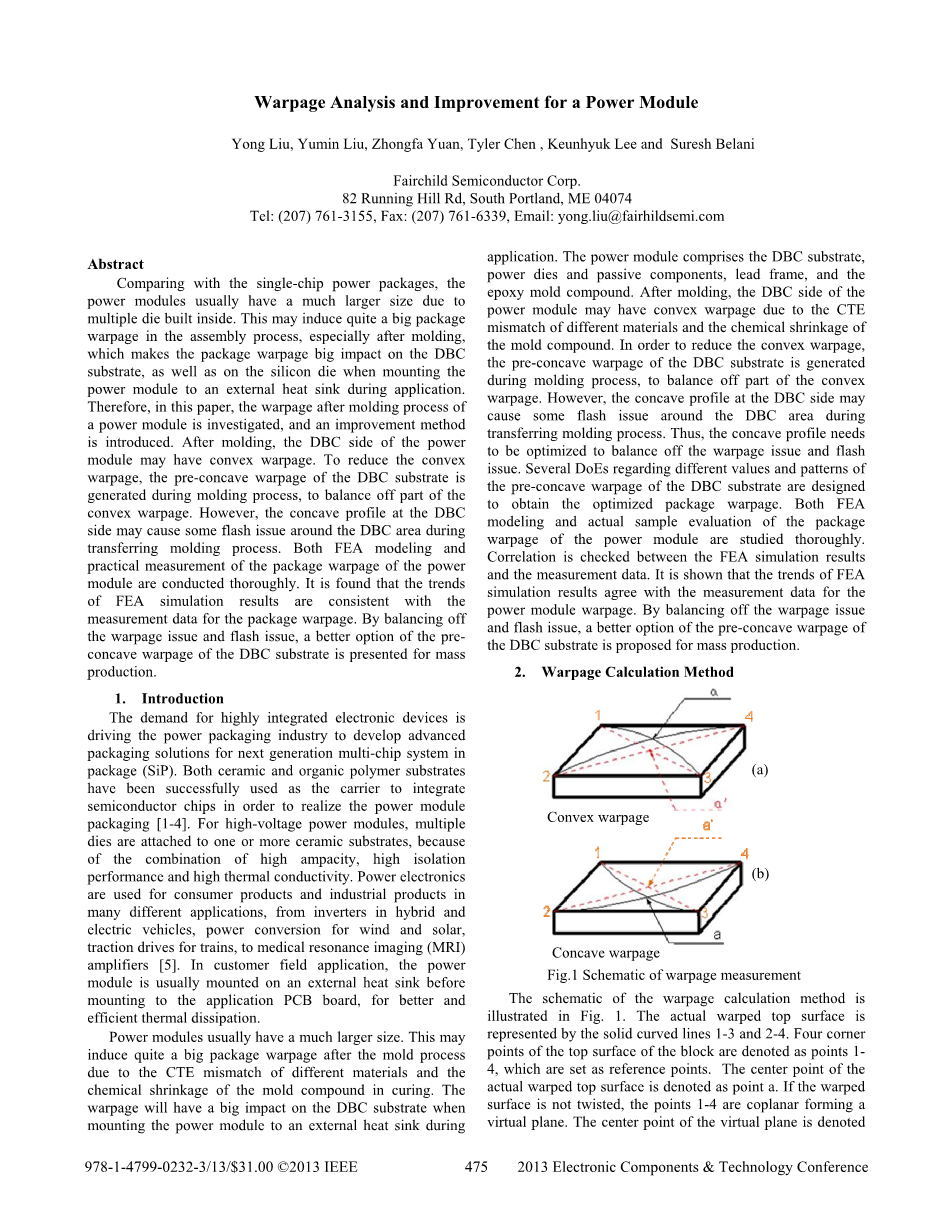

图1 翘曲测量示意图

翘曲计算方法的示意图如图1所示。实际的翘曲顶面由实心曲线1-3和2-4表示。块的顶表面的四个角点表示为点14,其被设置为参考点。实际翘曲顶面的中心点表示为点a。如果翘曲表面没有扭曲,则点1-4共面形成虚拟平面。虚拟平面的中心点表示为点a#39;,其与点线1-3和2-4的交叉点相同。如果翘曲曲面被扭曲,则点1-4不是共面的,并且点线1-3和2-4不能相交。在这种情况下,在点线1-3和2-4的中心获得两个虚拟交叉点(a#39;#39;和a#39;#39;#39;)。点a#39;被定义为点a#39;和a#39;#39;#39;的中点。块的翘曲定义为点a和点a#39;之间的垂直距离。假设功率封装的顶表面是DBC基板,图1(a)显示了DBC基板的凸翘曲,图1(b)显示了DBC基板的凹陷翘曲。在本文中,DBC基板的凸凹翘曲的定义都遵循这一规则。

3.翘曲建模的FEA分析方法

模塑过程后的封装翘曲可以假设为两部分的总和。第一部分是由于温度降低引起的不同材料的CTE不匹配引起的,第二部分是由塑封料在模具固化过程中的化学收缩引起的。封装翘曲的第一部分可以通过FEA常规建模来模拟。但第二部分很难通过FEA建模直接模拟。开发了一些等效方法,将许多研究人员将封装翘曲的第二部分纳入FEA建模[6-8]。在本文中提出了一种等效的CTE方法,通过FEA建模来模拟两个部件的封装翘曲。

等效CTE方法实际上是基于实际测量数据和FEA建模的相关性的经验CTE方法。对于特定封装,一些封装样品按照标准装配过程生产。然后测量每个样品封装的封装翘曲,并且基于所有样品的封装翘曲数据计算平均封装翘曲。同时,根据封装样品建立FEA模型,并且进行关于塑封料的不同CTE1(CTE低于Tg)值的试验设计以计算封装翘曲。结果表明,有通过FEA建模的模拟封装翘曲与实测数据吻合较好。将该情况下的塑封料的CTE1值作为等效的CTE1,既包括不同材料的CTE失配效应,也包括模具复合材料的化学收缩效应。

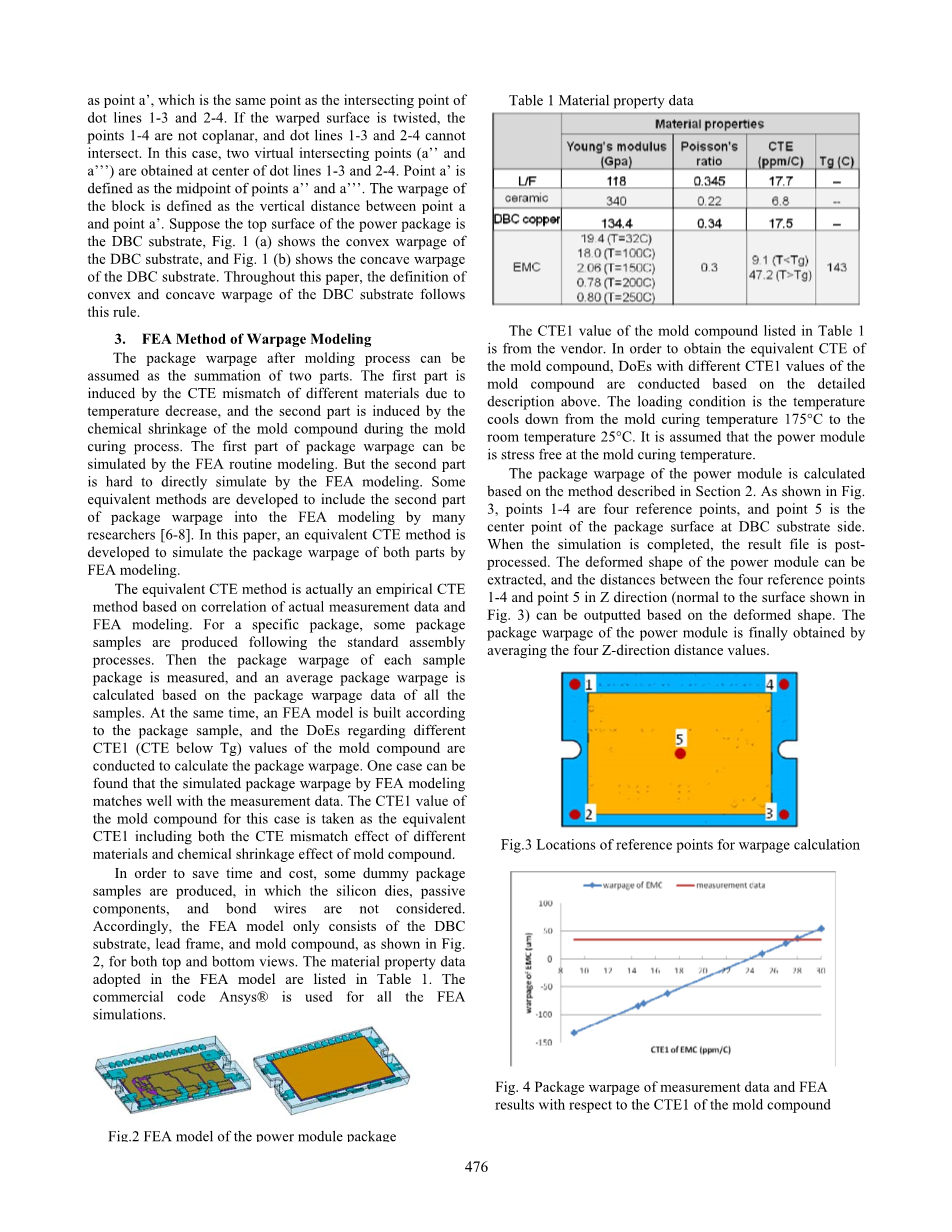

为了节省时间和成本,产生一些假片封装样品,其中不考虑硅管芯,无源元件和键合线。 因此,对于顶部视图和底部视图,FEA模型仅由DBC基板,引线框架和塑封料组成,如图2所示。 FEA模型中采用的材料属性数据列于表1.商业代码Ansysreg;用于所有FEA模拟。

图2 功率模块封装的FEA模型

表1材料属性数据

表1中列出的塑封料的CTE1值来自供应商。为了获得塑封料的等效CTE,基于上面的详细描述进行具有不同CTE1值的塑封料的试验设计。加载条件是温度从模具固化温度175℃冷却至室温25℃。假设功率模块在模具固化温度下是无应力的。

根据第二节中描述的方法计算功率模块的封装翘曲。如图3所示,点1-4是四个参考点,点5是DBC衬底侧的封装表面的中心点。模拟完成后,将对结果文件进行后处理。可以提取功率模块的变形形状,并且可以基于变形的形状输出四个参考点1-4和点5在Z方向上之间的距离(垂直于图3中所示的表面)。最后通过对四个Z方向距离值求平均来获得功率模块的封装翘曲量。

图3翘曲计算的参考点位置

图4测量数据和FEA结果的封装翘曲

相对于模塑化合物的CTE1,模塑料的CTE1为9.1~30ppm /C,共进行8个模拟实验组。 仿真结果如图4所示。可以看出,功率模块的封装翘曲与塑封料的CTE1成线性比例。 通过与功率模块的封装翘曲的测量数据进行比较,对于该特定功率模块,得到该特定功率模块对应的复合模CTE1为28ppm /C。 因此,该塑封料的CTE1值将在下面的功率模块FEA模拟中使用。

4. 由FEA 试验设计的翘曲改善

在模塑成型之后,功率模块的DBC侧可能由于不同材料的CTE不匹配和塑封料在固化过程中的化学收缩而具有凸出翘曲,如第3节的测量数据所示。封装翘曲将对DBC基板以及在应用期间将功率模块安装到外部散热器时,硅芯片也会受到很大影响。因此,提出了一种改进方法来减少封装翘曲。在模塑过程中,产生DBC基板的预凹翘曲,以平衡部分凸翘曲。为了优化模具固化后的封装翘曲,设计了关于DBC基板的预凹翘曲的不同值和形状的六个试验设计,如表2所示。DBC基板在二维预翘曲情况下的外表面呈球形,在一维预翘曲情况下沿长边呈圆柱形。预翘曲值是指当达到设计的预翘曲形状时DBC基板的中心点的移动距离。试验1显示没有DBC基板的预翘曲作为比较的实验组。试验2-5用于二维预翘曲DBC基板,其预翘曲值范围为80至150mu;m。试验6是DBC基板的一维预翘曲情况。

表2处理不同DBC的预翘曲

对于所有试验设计的模拟,采用与第3节中描述的相同的FEA方法。图5中示出了六种情况下功率模块的Z方向位移的模拟轮廓结果,其中还列出了每种情况下的封装翘曲。根据第2节和第3节中描述的翘曲计算方法计算功率模块的封装翘曲。图6示出了功率模块相对于不同的预凹翘曲值和DBC基板的轮廓的模拟封装翘曲。可以看出,功率模块的封装翘曲与DBC基板的一维预凹翘曲值成线性比例。随着DBC基板的预凹翘曲变大,在模具固化后,封装的更凸起的翘曲得到平衡。因此,导致较小的凸起封装翘曲。通过比较实验4和实验6,可以看出,在DBC基板的预翘曲值相同的情况下,一维预翘曲试验在模制过程之后产生更大的功率模块的封装翘曲。从功率模块的封装翘曲的角度来看,DBC基板的二维预凹翘曲轮廓比一维预凹翘曲情况具有更好的改善。

图5六个实验组在Z方向上的变形轮廓

图6所有六个功率模块的封装翘曲

表3中列出了DBC基板陶瓷在室温下的最大拉应力(S1)和压缩应力(S3)。由于FEA模型大大简化,因此应力值只能用于趋势分析。 通过比较所有六种情况,陶瓷中S1和S3的变化均为5%,即DBC基板的预翘曲对DBC基板的陶瓷中的应力没有显著影响。 因此,当限定DBC基板的预翘曲时,陶瓷基板中的感应应力不是重要因素。

表3 25℃下陶瓷应力模拟结果

5.翘曲测量的设置和结果

光学三维翘曲测量设备如图7(a)所示,用于翘曲测量的功率模块样品和夹具如图7(b)所示。 封装样品所在的夹具表面光滑平整。 通过调节光学设备的焦距,相对于位置点1-5处的平坦夹具表面的高度(如图3所示)可以读出为h1-h5。 根据第2节中的翘曲计算方法,图1a等于h5,a#39;等于h1-h4的平均值。 因此,可以将封装翘曲计算为a和a#39;的差值。

图7(a)翘曲测量设备,(b)样品和夹具

表4用于翘曲测量的功率模块样本

根据表4中列出的参数生成三组功率模块样品(实验组A,B和C)。封装翘曲的测量数据列于表5中。图6中的FEA模拟结果与表5的实测数据对比如图8所示。可以看出,FEA模拟的封装翘曲非常接近于DBC基板的一维预翘曲的测量数据。 对于二维预翘曲情况,FEA模拟翘曲值相对于翘曲前值的变化趋势与实际测量数据一致。 然而,来自FEA仿真的绝对封装翘曲值与实际测量数据之间存在一定的差距。将对FEA方法进行进一步的研究,以缩小这一差距。

表5封装翘曲的测量数据

图8 FEA结果与测量数据的比较

在注模塑的制程中, DBC基板由于预翘曲将与模具型腔产生间隙。 通常在模塑化合物填充之前在DBC基板的四个角处施加顶针,但是难以完全闭合间隙。 DBC基板边缘附近的间隙较大,由于传递压力,封装溢胶很容易脱落。 一维预翘曲设计的优点是可以使顶针更有效地减小DBC基板和模具型腔之间的间隙。 对功率模块样本的溢胶深度和长度进行监测,并且溢胶深度测量的位置如图9所示。对于三个实验组,表6和7中列出了DBC周围区域测量到的的最大溢胶深度和长度。值为100mu;m的二维预翘曲的C组DBC基板性能最好,一维预翘曲的B组和二维预翘曲的A组的DBC基板的的溢胶深度具有相当的控制水平。

图9封装固化后监测到的溢胶深度位置

表6最大溢胶深度的测量数据

表7最大溢胶长度的测量数据

在功率模块的应用中,它通过具有指定扭矩的螺丝刀组装到外部散热片上。 为了确认DBC基板和散热片之间的接触情况,将对压力敏感的压印纸放在DBC侧和散热器之间。 如图10左图所示,红色标记表示DBC基板和外部散热片之间的良好接触。 图10中黄色圆圈中具有较厚润滑脂区域的实际样品表明DBC基板和外部散热片之间的接触不良。 可以看出,压印纸标记方法与实际测试吻合较好,因此该压印纸方法可行且有效。 DBC基板上的三种情况下的压印纸标记如图11所示。可以看出C组具有更大的DBC接触面积。

图10压印纸痕与润滑脂对比图

图11 DBC基板上的三个压印纸痕标记

在分析过程中,C组产生最大的封装翘曲,但具有最高的Ppk值,即过程性能指数。 Ppk值即基础地尝试验证您从该过程生成的样本是否能够满足客户CTQ(要求)。它可用于短期的预生产运行。 Ppk的值大于1.67通常是可以接受的,越大越好。A组的Ppk值小于1.67,因此可以筛选出该组。从封装翘曲的角度来看,B组是A组和C组的中间情况。但是, B组在DBC区域周围产生比C组更厚的溢胶。通过压印纸标记分析,C组显示DBC基板和外部散热片之间的最佳接触。 因此,通过平衡封装翘曲问题和溢胶问题,建议将C组和DBC基板的二维预翘曲值设置为100 mu;m作为优化选项。

6.讨论和结论

通过FEA分析建模和实际测试测量,研究了功率模块封装过程后的翘曲。在FEA建模中,建立了等效CTE方法,考虑了塑封料的化学收缩和不同材料的CTE不匹配的影响。在实际测试中,采用光学三维翘曲测量设备对测量模具封装后功率模块的翘曲。通过产生DBC基板的预凹陷翘曲来引入翘曲改善方法。针对DBC基板预凹翘曲的不同值和形状,设计了几种不同的方法来获得优化的封装翘曲。

(1)功率模块的封装翘曲与DBC基板的二维预凹翘曲值成线性比例。随着DBC基板的预凹翘曲变大,在塑模固化后,封装的更凸起的翘曲得到平衡。因此,导致较小的凸包翘曲。

(2)根据FEA模拟结果,陶瓷基板中的诱导应力不是限定DBC基板的预翘曲的重要因素。

(3)根据实际测量数据,C组产生最大的封装翘曲,但具有最高的Ppk值,这表明更好的工艺性能。

(4)通过平衡封装翘曲问题和溢胶问题,建议将C组的DBC基板的二维预翘曲值设为100 mu;m作为优化选项。

致谢

作者感谢封装开发集团仙童半导体公司的支持。

外文原文

Warpage Analysis and Improvement for a Power Module

Abstract

Comparing with the single-chip power packages, the power modules usually have a much larger size due to multiple die built inside. This may induce quite a big package warpage in the assembly process, especially after molding, which makes the package warpage big im

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[424529],资料为PDF文档或Word文档,PDF文档可免费转换为Word