英语原文共 9 页,剩余内容已隐藏,支付完成后下载完整资料

多核系统中不同OpenMP调度技术的3D-DRAM性能

摘要——包括3DDRAM存储器在内的存储器技术的进步(例如高带宽存储器(HBM)和混合存储器立方体(HMC)系统),Wide I/O内存对于非常大的带宽和更低的功耗的保证,满足了高性能计算以及新兴的大数据应用程序的需要。然而,为了充分利用这种带宽,了解如何在内存结构的channel、rank、bank或存储库中优化地组织数据、如何以较少的访问量获取大量数据、以及如何安排多线程应用程序的线程,以便从这些内存结构中获益,就变得很有必要了。在本文中,我们将研究不同的内存结构,将数据分散到不同的channel、rank和bank中,并确定应用程序能从不同的内存结构中获得的好处。我们的研究适用于一般的DDR内存结构以及3DDRAM。我们还将评估OpenMP线程的调度(例如使用静态、动态和引导调度),但重点是不同的调度方法如何从不同的内存结构中获益。我们的实验表明,使用适合应用程序的最佳调度、适当的内存结构之后,能根据工作负载实现高达16%的性能提升。

索引——OpenMP、调度、内存结构、HBM

一、引言

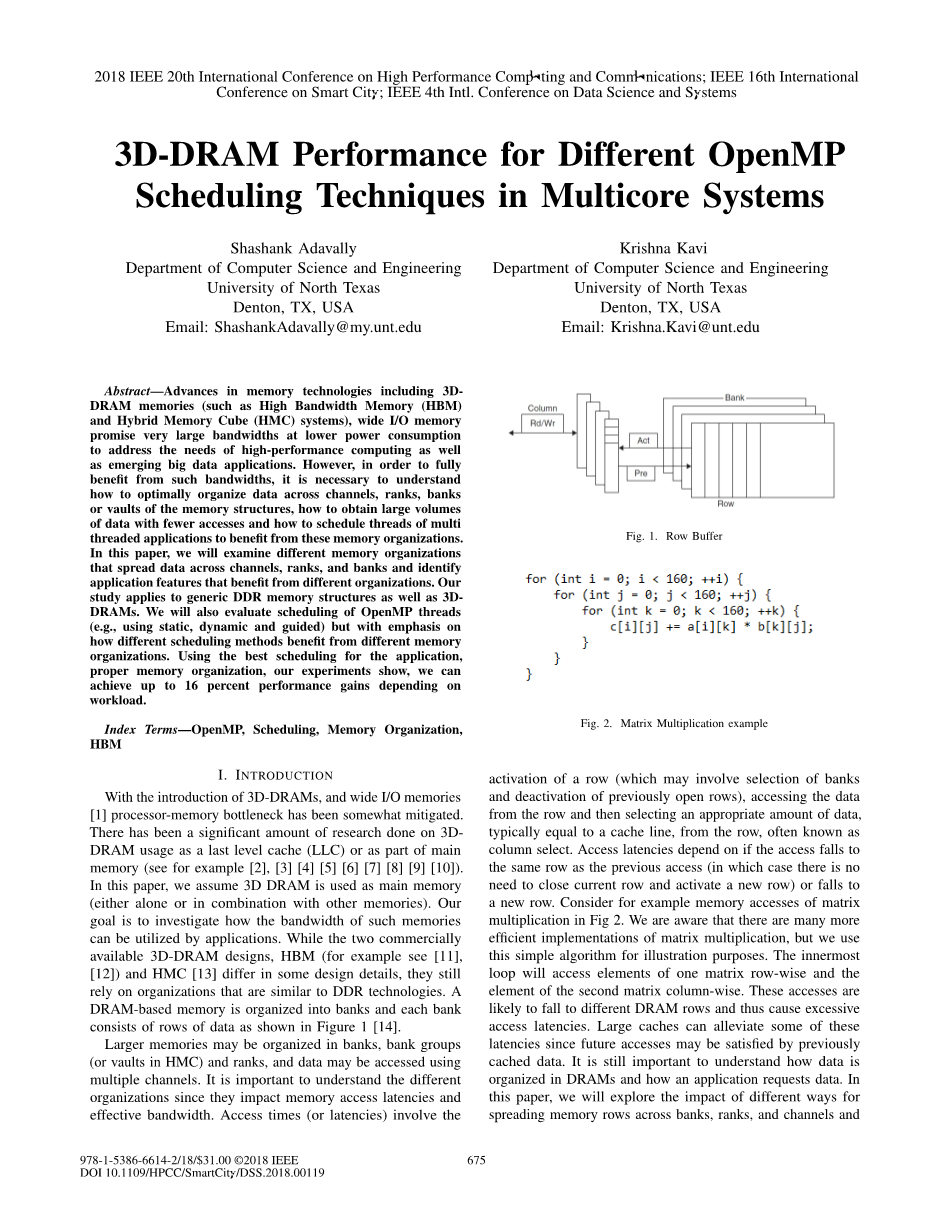

随着3D-DRAM的引入,Wide I/O内存的[1]处理器和存储器之间的发展阻碍有所缓解。对于3DDRAM作为最后一级缓存(LLC)或作为主内存的一部分的使用,已经进行了大量的研究(参见例子[2]、[3]、[4]、[5]、[6]、[7]、[8]、[9]、[10])。在本文中,我们假设使用3D-DRAM作为主存储器(单独使用或者与其他存储器组合使用)。我们的目标是研究应用程序如何例用这些内存的带宽。尽管两种商用的3D-DRAM设计——HBM(例子参见[11]、[12])和HMC[13],在某些设计细节上有所不同,它们仍然依赖于与DDR技术类似的结构。基于DRAM的内存被组织成多个存储组,每个存储组由数据行组成,如图1[14]所示。

图1 行缓冲器

较大的内存可以被组织在bank,bank组(或者HMC中的库)和rank中,并且可以通过多个channel访问数据。了解不同的结构非常重要,因为它们会影响内存访问延迟和有效带宽。访问时间(或延迟)包括激活一行(可能涉及选择bank和取消激活以前打开的行),从该行访问数据,然后从该行选择适当数量的数据,通常相当于来自行的缓存线,也称为列选择。访问延迟取决于访问的行是否与前一次访问的相同(在这种情况下,不需要关闭当前行并激活新行)或是新的行。例如图2中矩阵乘法的内存访问。我们知道矩阵乘法有许多更有效的实现,但是我们使用这个简单的算法来说明问题。最里面的循环将按行访问第一个矩阵的元素,按列访问第二个矩阵的元素。这些访问可能会落在不同的DRAM行上,从而导致访问延迟过大。由于以前缓存的数据可能会有利于以后的访问,因此大型缓存可以减少其中的一些延迟。了解如何在DRAM中结构数据,应用程序如何请求数据仍然很重要。在本文中,我们将探讨不同方式对跨bank、rank和channel分布内存行的影响,以及由此产生的内存访问性能问题。

图2 矩阵乘法示例

如果在多核系统上执行多线程应用程序,内存性能取决于不同线程如何访问数据(以及数据如何分布在DRAM的bank、rank和channel)。如果来自不同线程的访问落在不同的行中,访问可能会对内存延迟产生负面影响。多线程应用程序的访问行为,特别是使用OpenMP[15]编写的应用程序,可以通过决定如何给循环迭代(使用pragma omp parallel for时)分配给线程来控制。例如,连续迭代可以分配给同一个线程(区块调度),也可以循环分配给不同的线程(循环调度)。而这些不同的方法会导致线程访问不同的行或同一行。在本文中,我们将探讨在使用DRAM或3DDRAM设备时,OpenMP调度如何影响内存访问性能。

关于近数据处理(NDP)或内存处理(PIM)方法,已有许多研究(例如[16][17][18][19][20][21]),通过这些方法,将计算移近内存,以克服长内存延迟和使用大带宽问题。当处理元素嵌入到3D-DRAM的逻辑层中时,由于这些系统不受总线宽度或管脚计数的限制,因此可能在每次访问(而不是每次一条缓存线)时获得更大的数据量。另一方面,如果连续访问落在不同的行上,这将是浪费。此外,PIM(内存中处理)元素可能非常简单,没有或限制缓存的有序内核。因此,了解按顺序内核的内存访问是否与不按顺序内核的内存访问不同,并确定哪个线程调度更适合PIM设计(与主机CPU的调度相比)。

在这项研究中,我们研究了影响内存性能的三个相关问题(例如平均访问时间):i)DRAM行如何分布在bank、rank和channel中,i i)如何将循环迭代分配给OpenMP线程以及线程如何访问数据,以及i i)PIM设计是否能从3D-DRAM技术中获益。

我们使用两种类型的CPU内核进行实验:具有大型多级缓存的大型无序内核,以及只有小型一级缓存的简单有序内核。由于3D-DRAM设备的电源限制,第二种类型的内核可能是内存实现处理的选择。正如我们将在本文中报告的那样,在“最佳”内存性能中哪种内存结构和哪种线程调度结果,取决于所使用的核心类型(无序或有序)。因此,本文的主要贡献在于理解不同的内存结构、不同的线程调度方法和不同类型的内核如何在应用程序的内存访问性能中发挥作用。

论文的其余部分结构如下。在第二节中,我们将详细介绍如何组织DRAM内存。我们将讨论如何调度OpenMP中的线程。本节概述了本文的工作,并介绍了我们的实验方法,包括我们使用的模拟环境和基准集。在第三节中,我们将介绍我们的实验结果和结果分析。在第四节中,我们将讨论这项工作的潜在扩展。第五节简要概述了与本研究相关的一些工作。最后,第六节包含了对这项工作的总结的高层次见解。

二、方法论

A. 地址映射

地址映射描述了DRAM内存中跨channel(或HMC中的库)、rank、bank、行和列的数据分布。如果内存结构是RoBaRaCoCh(如图4所示),那么数据将分布在channel、行、bank、bank组和rank中,以组成一行。也就是说,一个DRAM行的数据分布在bank、bank组、rank和channel中,从而导致每行访问的数据量非常大,例如256K字节。如果连续访问属于同一行,并且可以开放这一行满足这些访问,则此结构非常有用。例如,考虑图2,计算c[i][j] =a[i][k]*b[k][j]的矩阵乘法的最里面的循环。在这种情况下,对矩阵“a”的访问将落在同一行,但对“b”的访问将落在不同的行(假设矩阵非常大)。如果结构是ChRaBaRoCo,如图3所示,数据分布在同一行中的一系列行中,因此每一行要小得多,例如,2K字节。现在需要128行访问才能获得与前一个结构中相同数量的数据;需要注意的是,访问新的DRAM行需要关闭前一行(并将该行写回DRAM)并打开新行。虽然该结构可能有利于矩阵乘法中对“b”矩阵的访问,但它可能会使对“a”矩阵的访问处于不利地位。可以依赖其他架构优化(如预取)来进一步优化内存性能。

B.内存结构的类型

商用处理系统允许基于DIMM大小的内存结构。它们允许跨多个DIMM、channel和节点分布数据(或交错物理地址),限制对单个DRAM行的访问[22]。我们认为有可能利用这些地址互换来实现本文所研究的两个结构。虽然我们没有明确提出覆盖不同3D DRAM的结构(如库),但被评估的两个结构旨在探索两种极端情况,一种是提供非常大的行去覆盖所有channel、rank、库等,而另一种是包含在bank(或库)内的非常有限的行大小。我们现在提供更多关于这些结构的详细信息。

1. ChRaBaRoCo:

我们选择这个结构是因为它不具有任何类型的bank或channel级别的并行性。每一行都包含在一个bank中。对于图形视图,请参见图3,它显示了如何将31位地址分割到DRAM的结构中。正如可以看到的,DRAM行只分配给一个channel,不能从多个channel的存在中获益。3D-DRAM设备可能有多个channel,在一些设计中多达32个。如果不同线程(或任务)的访问可以分布在不同的channel上,则此结构可能更适合于多任务或多线程应用程序。另一方面,对于单线程应用程序,此结构不使用channel级并行,可能导致内存性能降低。

图3. ChRaBaRoCo

2. RoBaRaCoCh:

此结构跨多个channel传播行以利用channel级别的并行性(更快地获取数据),有关图形视图,请参见图4,图4显示了如何将31位地址拆分为DRAM结构。现在使用多个channel访问单个DRAM行中的数据。此结构可能会导致多线程和多任务工作负载的内存访问冲突。我们了解到,这个使用多个channel获取大量数据的结构目前尚未在商业系统中实现,但我们希望探索多核系统的潜在效益。在一个典型的商业DDR系统中,一个channel负责从一个或多个rank和bank传输数据(类似于图3中的结构)[22]。但是,内存控制器能够对来自不同的rank和bank的行进行对齐,以便所有channel都能用于传输数据,从而有效地实现图4中显示的结构。请注意,我们的模型只包含一个rank,因此,图3和图4中没有rank位。

图4. RoBaRaCoCh

其他结构可能会导致每行访问的数据量不同、channel级并行度和rank级并行度不同。其中一些结构可以使用3D-DRAM,即使它们对2D DDR内存没有意义。但是,我们将研究局限于本文所描述的两个结构,因为它们代表数据分布的两个极端情况。

C.调度

在多核处理器和许多核GPU的时代,高效的并行编程对于从这些系统中获益至关重要。为了我们的目的,我们将研究局限于同构多核系统,因此将重点放在OpenMP风格的程序上。由于程序员可能不知道DRAM结构(如上文所述),这些并行程序可能无法达到最佳性能水平。例如,很少有程序员在OpenMP中使用“schedule”子句(即,没有指定的调度类型),依靠运行时系统来实现调度。使用“schedule”子句,与不使用“schedule”子句相比,对总体性能造成最大3倍的特定工作负载影响。有些程序员使用静态块调度,将连续迭代的数字(即块)分配给同一线程。也可以使用其他方法将循环迭代分发给线程,包括循环地将迭代分配给线程(在这种情况下,可以将连续迭代分配给不同的线程)。在动态调度中,循环迭代块被分配给下一个空闲线程,这可能导致分配给不同线程的迭代次数不均匀。在引导式调度中,最初只有一部分(通常是一半)的工作被分配给线程,当分配的工作完成时,迭代的另一部分被分配,直到所有的工作都完成。这种调度类型可以减少块的大小,以提高迭代之间的负载平衡。最后,当指定auto时,迭代调度分配由编译器控制。虽然循环迭代的循环分配通常不用于动态和引导式调度方法,但我们在本研究中探讨了此类分配。显然,使用的调度会影响应用程序的性能,因为不同的调度方法会导致不同的内存访问模式。我们的目标是定量测量由于线程调度和DRAM内存结构导致的性能差异。在某些情况下,来自不同线程的访问会落在同一个DRAM行中,而在其他情况下,它们落在不同的DRAM行中。DRAM行的大小和分布会影响访问延迟。本文主要研究两种不同的迭代分布方法(分块和循环),三种调度方法(静态、动态、引导)和两种DRAM结构。在前面研究了OpenMP调度对性能的影响的同时,重点研究了不同内存结构的调度方法对内存访问的影响。我们还研究了这些结构和有序和无序核心的调度方法,因为PIMS可能会在有序核心中使用。

|

处理器 |

参数 |

|

内核数 |

4 |

|

类型 |

有序 |

|

频率 |

1.0GHz |

|

高速缓存 |

参数 |

|

L1 大小 |

32K |

|

共享L2 大小 |

64K |

|

关联方式 |

4 |

表1. 类似PIM的核心和缓存配置

|

处理器 |

参数 |

|

内核数 |

4 |

|

类型 |

无序 |

|

频率 |

3.5GHz |

|

高速缓存 |

参数 |

|

L1 大小 |

32K |

|

关联方式 |

8 <!--全文共19528字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[2324] |

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。