英语原文共 5 页,剩余内容已隐藏,支付完成后下载完整资料

数据通信系统低功耗无时钟串行链路的设计与建模

Mohammed H. Alser

电气和电子工程Universiti Teknologi PETRONAS Perak Darul Ridzuan,Malaysiamealser@gmail.com

Maher M. Assaad

电气和电子工程Universiti Teknologi PETRONAS Perak Darul Ridzuan,Malaysiamaher_assaad@petronas.com.my

摘要 - 由于集成电路技术的不断进步,SoC(片上系统)正变得越来越大,需要许多互连SoC模块的长片上线。然而,在高速模块之间同步且可靠地传送同步数据变得越来越具有挑战性。因此,要利用增加的模块的可用处理速度并提高整体系统性能,需要高速通信网络。本文概述了在当今基于多模块的SoC中使用多位传统总线作为同步通信介质的相关问题和限制,并提出了异步串行链路作为潜在的高性能替代解决方案。此外,它回顾了当前最先进的串行链路,并提出了一种基于四分之一速率概念的新架构,最终将导致在SoC中实现低功耗和高速的模块间链路。

关键字 - PLL,CDR,SerDes,串行链路。

I. 绪论

现代集成电路(IC)技术成功的秘密在很大程度上归功于在小型半导体晶圆上实现大规模电子系统的低成本。多年来,IC制造技术的进步使IC的速度和集成度呈指数级增长。上述这些进步使得集成晶体管的数量比集成芯片的输入和输出(I / O)引脚的数量快得多。虽然英特尔最新一代处理器称为“Sandy Bridgetrade;”,其中包含超过11.6亿个晶体管,并且按照摩尔定律每两年继续增加一倍,但I / O引脚的速度性能历史上大约每六年翻一番。

此外,随着芯片处理速度的提高,芯片之间更高通信带宽的需求也在增长。早在1997年,D.Matzke [1]就基于物理事实发表了他自己的预测,这些事实将限制SoC处理速度的进一步改进,特别是由于电线缩放而需要长距离和快速交互的架构。导线不能很好地扩展,因为导线之间的间距必须继续缩小,因此导线可以连接到较小的晶体管。随着片上导线横截面缩小,每单位长度的导线延迟将增加。因为电阻与电线的横截面成反比。

但是,模块之间的通信带宽跟不上模块性能;这导致模块的处理速度和模块间通信带宽之间的差距越来越大。鉴于开发改进的片上互连以维持超大规模集成(ULSI)密度和性能趋势的至关重要性,继续忽视这一差距变得越来越困难,这会影响整体系统性能。

II. 研究现状

先前已经提出片上串行链路作为降低片上互连结构的复杂性和/或能量耗散的强有力的解决方案。但是,人们注意到,在单个互连上串行化m位会增加整体数据切换活动[2]。因此,本研究的主要挑战之一与提出一种新架构有关,该架构最终将导致在SoC中实现低功耗和高速模块间链路。

A. 研究范例

单个芯片中结合的晶体管数量的急剧增加导致了SoC的设计概念。目前,SoC设计变得越来越复杂,越来越多的模块被集成到单个SoC设计中。这些模块通常需要通过片上通信架构相互通信。这些模块之间的通信成为性能瓶颈的根源。

多年来,基于总线的范例是数据通信系统中最常见的范例。图1显示了多位传统总线架构,其中各种模块通过一组共享的并行线互连。另外,将单独的导线分配给承载用于同步发送和接收数据的全局时钟信号的所有模块。

图1:SoC中传统的基于总线的通信。

尽管这种通信范例在过去已经足够,但增加的速度突出了与使用多位传统总线系统相关的几个问题[3]。由于总线承载的数据信号必须与全局时钟信号同步,因此偏斜已经成为增加工作频率以及相邻总线之间串扰的主要限制,这产生了重要的限制;导致数据信号延迟和噪音。这对数据传输的长度设置了上限,因此使得片上通信不可靠。此外,添加更多模块会导致每个二进制转换的能量耗散增加,并且由于更高的容性负载而降低整体系统速度。使用总线的成本也是一个严重的问题,因为它们占据了大面积的硅。因此,利用全局时钟将多位总线用于片上通信将限制未来SoC的进一步改进。

多位传统总线的物理和电气限制使其仅适用于包含少量模块的小型系统,例如存储器或外围总线。对于诸如多处理器或通信交换机之类的大规模系统,另一种有吸引力的解决方案是通过点对点链路替换总线作为通信媒介。从电路和架构的角度来看,这种方法具有优势。从电路设计的角度来看,由于信号完整性问题减少,点对点链路具有比总线更高的通信带宽。此外,点对点传输线在系统的物理构造中提供了更大的灵活性。从架构的角度来看,高速系统的带宽需求使共享总线介质成为主要的性能瓶颈。

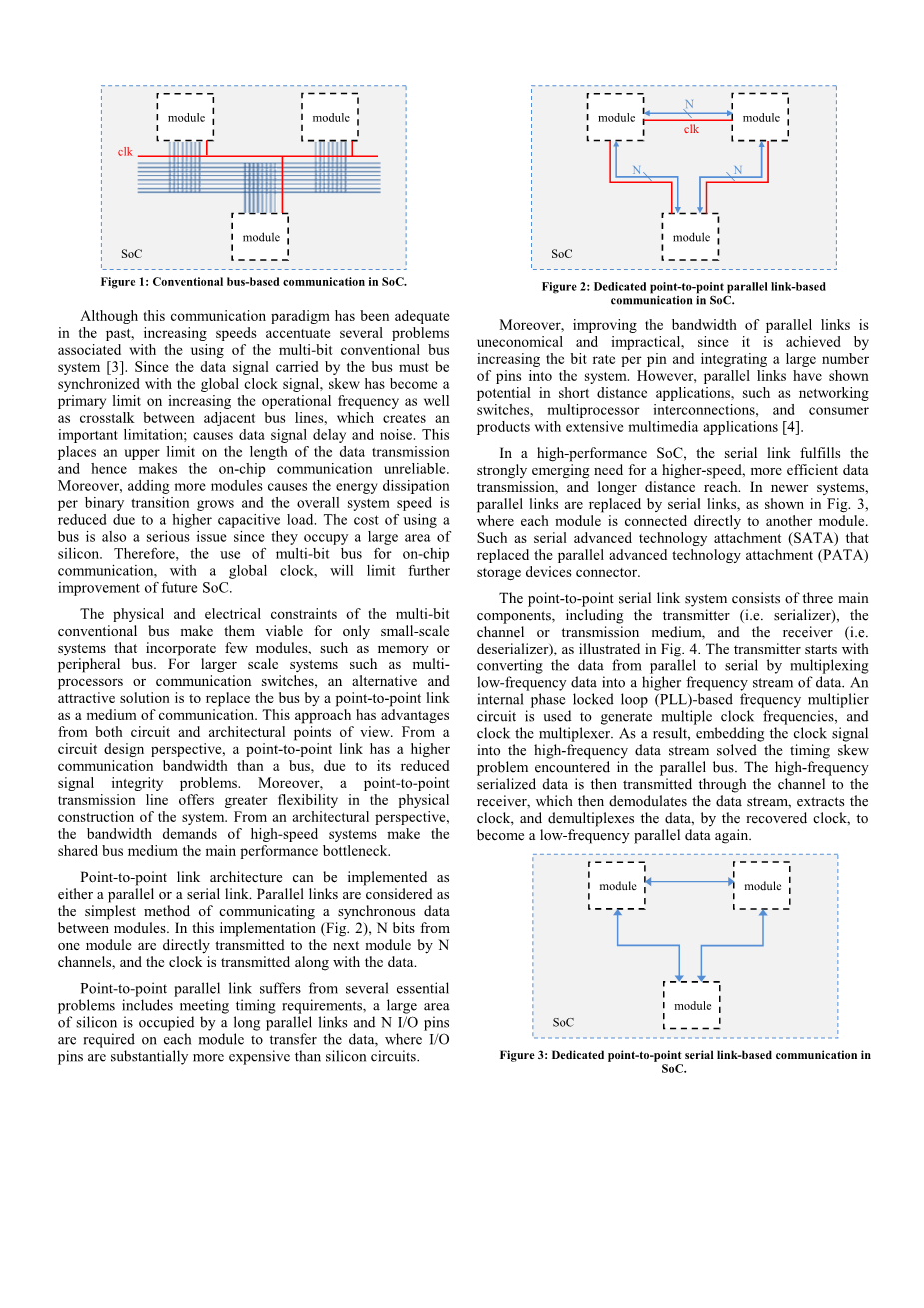

点对点链路架构可以实现为并行或串行链路。并行链接被认为是在模块之间传递同步数据的最简单方法。在该实现中(图2),来自一个模块的N个比特通过N个信道直接发送到下一个模块,并且时钟与数据一起发送。

点对点并行链路存在几个基本问题,包括满足时序要求,大面积的硅被长并行链路占用,每个模块都需要NI / O引脚来传输数据,其中I / O引脚是比硅电路贵得多。

图2:SoC中基于点对点并行链路的专用通信。

此外,改善并行链路的带宽是不经济和不切实际的,因为它是通过增加每个引脚的比特率并将大量引脚集成到系统中来实现的。然而,并行链路已经在短距离应用中显示出潜力,例如网络交换机,多处理器互连以及具有广泛多媒体应用的消费产品[4]。

在高性能SoC中,串行链路满足了对更高速,更高效的数据传输和更长距离范围的强烈需求。在较新的系统中,并行链路被串行链路取代,如图3所示,其中每个模块直接连接到另一个模块。如串行高级技术附件(SATA)取代了并行高级技术附件(PATA)存储设备连接器。

点对点串行链路系统由三个主要部分组成,包括发送器(即串行器),信道或传输介质,以及接收器(即解串器),如图4所示。发送器从转换开始通过将低频数据复用到更高频率的数据流中,从并行到串行的数据。基于内部锁相环(PLL)的倍频器电路用于产生多个时钟频率,并为多路复用器提供时钟。结果,将时钟信号嵌入到高频数据流中解决了并行总线中遇到的时序偏差问题。然后,高频串行数据通过信道传输到接收器,然后接收器解调数据流,提取时钟,并通过恢复的时钟对数据进行解复用,以再次成为低频并行数据。

图3:基于专用点对点串行链路的通信的SoC。

图4:串行链路的简化顶级框图

2007年国际半导体技术发展路线图(ITRS)预测,到2019年,高速点对点串行链路的数据速率将达到100-Gb / s .Gb / s数据范围意味着噪声数据和时钟接收器侧的信号。由于时钟嵌入在数据流中,时钟和数据恢复电路(CDR)必须以等于数据速率的频率从中提取时钟信号,将其传递给判决电路(通常是D触发器)以生成具有较少抖动和偏斜的良好定时数据。

文献介绍了主要的常用CDR拓扑结构:使用反馈相位跟踪的拓扑结构(包括基于PLL的拓扑结构)和没有反馈相位跟踪的拓扑结构。基于PLL的主要依赖于相位检测方法,该方法可以实现为全速率或半速率。基于PLL的全速率CDR将数据转换与时钟的下降沿或上升沿进行比较,其频率等于数据速率,但半速率CDR将数据转换与时钟的下降沿和上升沿进行比较,这意味着一半数据速率。使用半速率相位检测器具有减少所需时钟而无需额外电路的优点。另一方面,没有包括过采样的反馈相位跟踪的拓扑结构不能恢复时钟信号,但它可以恢复数据。这些拓扑使用更高的时钟频率在多个位置对数据流进行采样,并且在没有可用的专用硬件块时通常用于可编程设备。

目前,串行链路是任何应用的选择设计,其中通信信道的成本很高并且大量复制链路是不经济的。其应用跨越通信和网络应用的每个部分,其使用高速帧内/芯片间通信,包括但不限于光通信网络,计算机到外围设备连接,存储器总线和磁数据存储设备。

虽然串行链路中的数据速率很高,但速度不是唯一的目标,因为在需要高功率效率的系统中不能忽略其他要求,如功耗。M. Ghoneima [2]已经表明,先前已经提出片上串行链路作为降低片上互连结构的复杂性和/或能量耗散的有力解决方案。但是,注意到在单个互连上串行化m位会增加整体数据切换活动。Ghoneima在最近的一项研究[5]中表明,如果在保持相同信道区域的情况下减少信道数量。与64位并行链路通道相比,32个串行链路通道可以实现功耗的显着节省。由于增加了沟道宽度和间距,减小了相邻线路之间的耦合电容。因此,50纳米技术的能耗降低高达31.42%,随着技术的不断扩大,能源消耗将会增加。由于串行链路由于引脚数量减少而占用的空间较少,因此可以使用保存的区域将链路与周围组件隔离得更好,并集成更多模块。

B. 相关资料

在当前最先进的技术中,高速串行数据链路通信迅速普及,因为它具有优于并行链路的显着优点。

R. Dobkin进行了一项相对分析性研究[6],其中扩展了之前的研究[7],表明当考虑远程通信时,串行链路的性能优于并行链路。

图5:(左)最小链路长度,高于该链路长度,串行链路消耗的动态功率小于并行链路,(右)最小链路长度,高于该链路长度,有源区域和串行链路的泄漏小于并联链路。

此外,他预测串行链路对未来技术中的短链路将更具吸引力。由于未来的大型SoC设计应采用串行链路来降低面积,比特率,功率和延迟方面的通信成本。图5示出了对于任何特定技术节点,存在链路长度的限制值,高于该限制值,最好将链路实现为串行而不是并行,因为它在功率和面积方面更有利。

这促使在过去十年中进行了广泛的研究,以填补先前技术水平与最低功耗目标之间的差距。可提供最先进的节能串行链路,如下所示:

在[8] H. Yamaguchi等人中,提出了一个5-Gb / s串行链路,用于传输312.5-Mb / s 16位并行数据,总功耗为280-mW。

在[9]中,B。Drost显示从输入的2.5 Gb / s 4位并行数据以10 Gb / s运行的串行链路,总功耗为30 mW,接收器是延迟锁定环(DLL )基于CDR并以2.5-Gb / s的速度从链路中出来。

在[10] M. Hsieh,设计了一个单芯片串行链路,用于多标准应用(即SATA),速率从1 Gb / s到8.5 Gb / s,并支持425 Mb / s并行数据总线宽度为8,10,16和20位。接收器是半速率基于PLL的CDR。他介绍了最常用的CDR架构的概述和比较研究,表明CDR拓扑的最佳选择取决于应用和规范要求。

在[11]中,提供了使用两个ADC的12.5-Gb / s串行链路,每个串行链路的运行速率为6.25-Gb / s,总功耗为330-mW。接收器是基于PLL的半速率CDR,工作时钟速度为3.125-GHz。

在[12]中,S. Cheng提出了10-Gb / s串行数据链路,并重点介绍了PLL架构的设计,该架构在发送器侧实现为倍频器,在接收器端实现为CDR的形式。他研究了当时现有的CDR架构,并提出了基于半频率PLL的CDR架构,工作频率为5 GHz,总功耗为250 mW

在[13]中,J。Teifel模拟了用于芯片间通信的无时钟串行链路,它使用异步令牌环来控制数据复用和解复用以确定位边界,而不是产生多相时钟,这称为三通道协议。三通道协议是在1996年提出的,并且具有两个连续脉冲不会在同一通道上发送的特性,因为8位并行数据是通过三通道互连传输的。该链路的

全文共8219字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[186],资料为PDF文档或Word文档,PDF文档可免费转换为Word

您可能感兴趣的文章

- 拟人手臂的轨迹规划与轨迹跟踪控制外文翻译资料

- 新型磁性辅助内窥镜系统在上消化道检查中应用的可行性 和安全性外文翻译资料

- 基于FPGA可编程逻辑器件的复合视频图像处理外文翻译资料

- 从被测的高频域原始信号中提取巴克豪森噪声外文翻译资料

- 重型机床z轴热误差混合建模方法外文翻译资料

- 一个红外浊度传感器:设计与应用外文翻译资料

- 用于控制食物烹饪过程的电子系统.外文翻译资料

- 关于液体介质中电磁流量计的设计和理论上存在的问题。第二部分:关于带电粒子产生的 噪声理论外文翻译资料

- 基于LabVIEW和Matlab的小波变换对非平稳信号的分析仿真外文翻译资料

- 应用于腹腔镜手术的新型膜式加热加湿器 的开发外文翻译资料