英语原文共 8 页,剩余内容已隐藏,支付完成后下载完整资料

一种新型SOI单片电容传感器和绝对压差测量

- D. Dimitropoulos , C. Kachris , D.P. Karampatzakis , G.I. Stamoulis

雷神传感器,MEMS部门,Stratigi Str 7号。希腊雅典N通灵学院154 51,希腊b塞萨利大学计算机和通信工程系,格拉瓦尼海峡37号。希腊沃洛斯38221

2004年9月13日收到;2005年2月22日收到的修订表格;2005年3月3日接受

2005年4月28日在线提供

摘要

在目前的工作中,一种新的单片电容式压力传感器正在进入人们的视野。传感器是为客户量身打造的,有15项SOI工艺过程。就传感器设计而言,该过程主要提供了很大的灵活性。通过简单地布置相适合传感器的封装使绝对压力或压差的感测具有了可能性。测量的灵敏度和量程可以在很大范围内随意调节,通过设置单个设计参数来设置数值,注意避免p - n结的形成,以便提高传感器的稳定性,防止温度升高,同时允许高温后处理且不降低掺杂分布。所介绍的设计允许普通P阱CMOS后处理的实现。灵敏度为2 mV/kPa,量程为180 kPa (2% ),带宽为25 kHz,这里可以通过已发展并逐渐成熟的CMOS开关电容ASIC来实现。对ASIC的性能已经尽可能少地依赖CMOS工艺和晶体管参数变化,这种参数变化是因为晶体管衬底的较差的稳定性所引起的。而且实现了最先进电路的设计,以提高电路的稳定性、避免寄生电与感测电容器并联。额外模拟信号处理的实现在很大程度上提高了上述过程精度。传感器的主要应用包括医疗设备,如血压计和呼吸器,都需要很高的可靠性和生物相容性。

2005年Elsevier保留所有权利。

关键词:压力传感器;电容传感器;单片传感器;互补金属氧化物半导体

1 .介绍

15年前,集成压力传感器作为商业产品出现,从那时起,发现了许多汽车、航空、工业和生物医学应用。绝大多数这类系统的功能是基于压阻效应的,主要是由于以下事实。首先,压阻传感器不需要形成密封的空腔就能工作。这一事实在很大程度上简化了传感器的制造,同时已经建立了体积和表面微加工工艺,可以用来释放弹性硅膜片。其次,压敏电阻通过这种硅膜片上的标准CMOS工艺得到了发展。压阻传感器遭受严重的温度不稳定性是由于电阻率系数对温度的遗传依赖性以及电阻温度系数的错配。此外,其缺点还与压阻传感器相关,缺点主要包括重复性误差和高功耗。电容式压力传感器克服了这种困难,显示出优异的温度稳定性、可重复性和低功耗。不幸的是,这种传感器需要密封腔的发展,这种传感器需要结合一对绝缘导体才能工作。虽然这里有一系列表面微加工技术,能够形成密封腔,但很少能有效地与集成微系统的标准集成电路制造工艺相结合。另一方面,在CMOS预处理的情况下,传感器必须能够经受住高温制造步骤。在极少数的过程中,集成电路和传感器开发步骤的有效混合是可以实现的的。不管怎样,传感器和IC的单片结合几乎是强制性的,因为引线键合寄生电容引起的误差通常高于传感器信号本身。在目前的工作中,我们提出了一种新的集成压力传感器,它由一对SOI晶片按照15步工艺制成;SOI技术确实在表面微加工方面提供了显著的优势。所提出的设计允许p阱CMOS后处理。这里还介绍了用于传感器信号调节的开关电容ASIC。采用稳健的IC设计,以应对因衬底均匀性差而导致的晶体管参数变化增加。在180 kPa (2% )的压力范围和25 kHz的带宽内,可以实现2 mV/kPa的灵敏度。本系统(集成传感器和集成电路)可用于绝对和/或差分压力传感应用。此外,所提出的工艺流程的细微差别允许开发具有增加的线性度的触摸模式电容式压力传感器。基于标准集成电路制造步骤以及VLSI ASIC的工艺流程最初是由作者开发的,并在此介绍。系统原型由德国[埃尔富特的XFAB半导体制造。

2 .传感器设计和制造

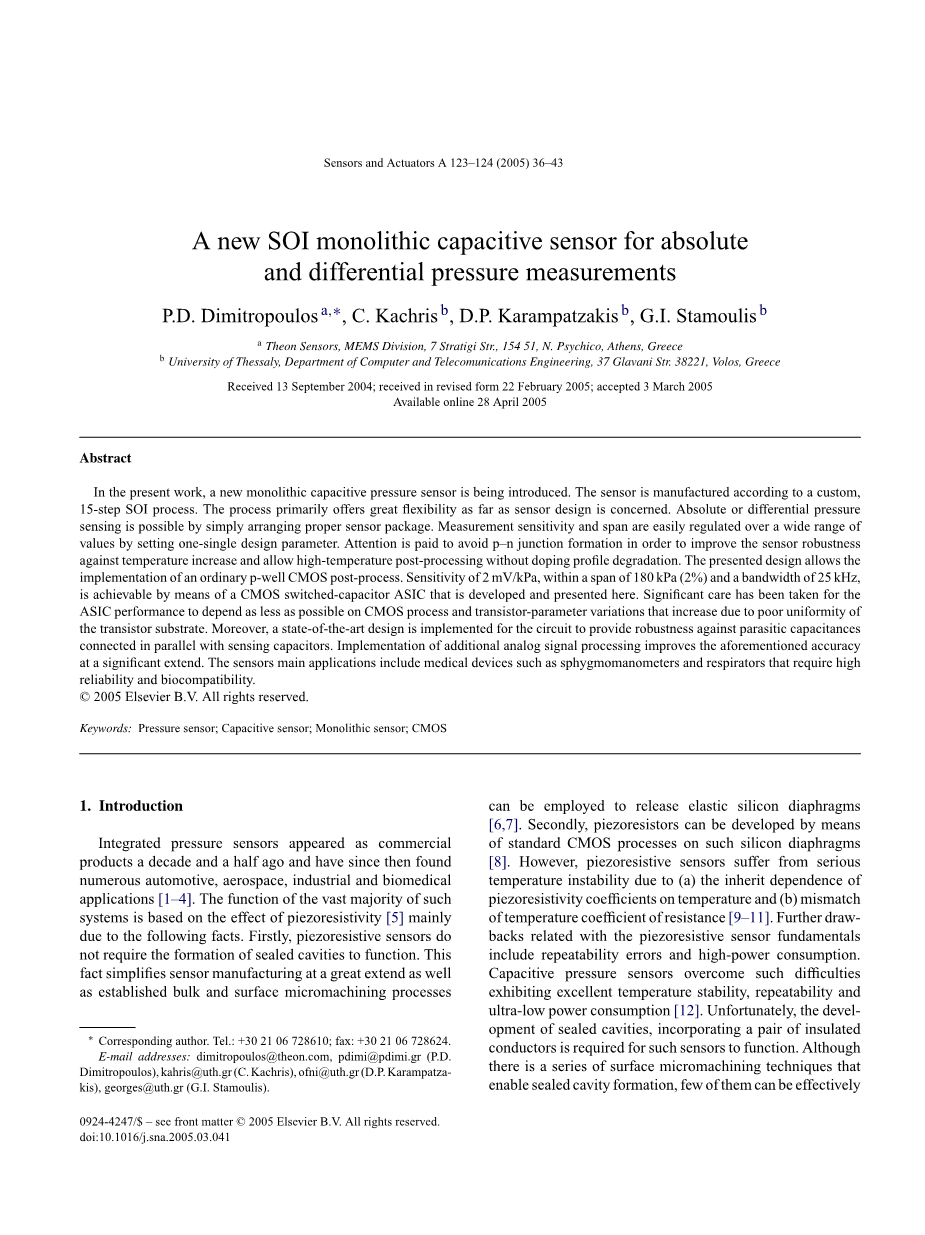

传感器由两个具有custom维度的SOI晶片A和B制成,这两个晶片结合在一起,随后被研磨、蚀刻和抛光。两个晶片都包含3mthick器件层( DL ),其通过0.1m厚的去毛刺二氧化硅( BO )层与外体( B )分离。通过热扩散和随后注入P原子,两个晶片的器件层被掺杂( n型),浓度为1017 cm - 3,用于形成上部( UC )和下部( LC )感测电容器导体。由于晶片B的DL层在CMOS后处理期间用作晶体管衬底,因此需要大量的后退火过程,以获得器件层的电特性的均匀性。晶片和B的BO层用作扩散阻挡层,在高温后处理步骤如thermal氧化、晶片键合和晶体管形成期间保护掺杂轮廓。接下来,通过热氧化在水A的表面上形成1m厚的二氧化硅层( TO )。晶片和B的制备如图1所示

图1SOI晶片的制备

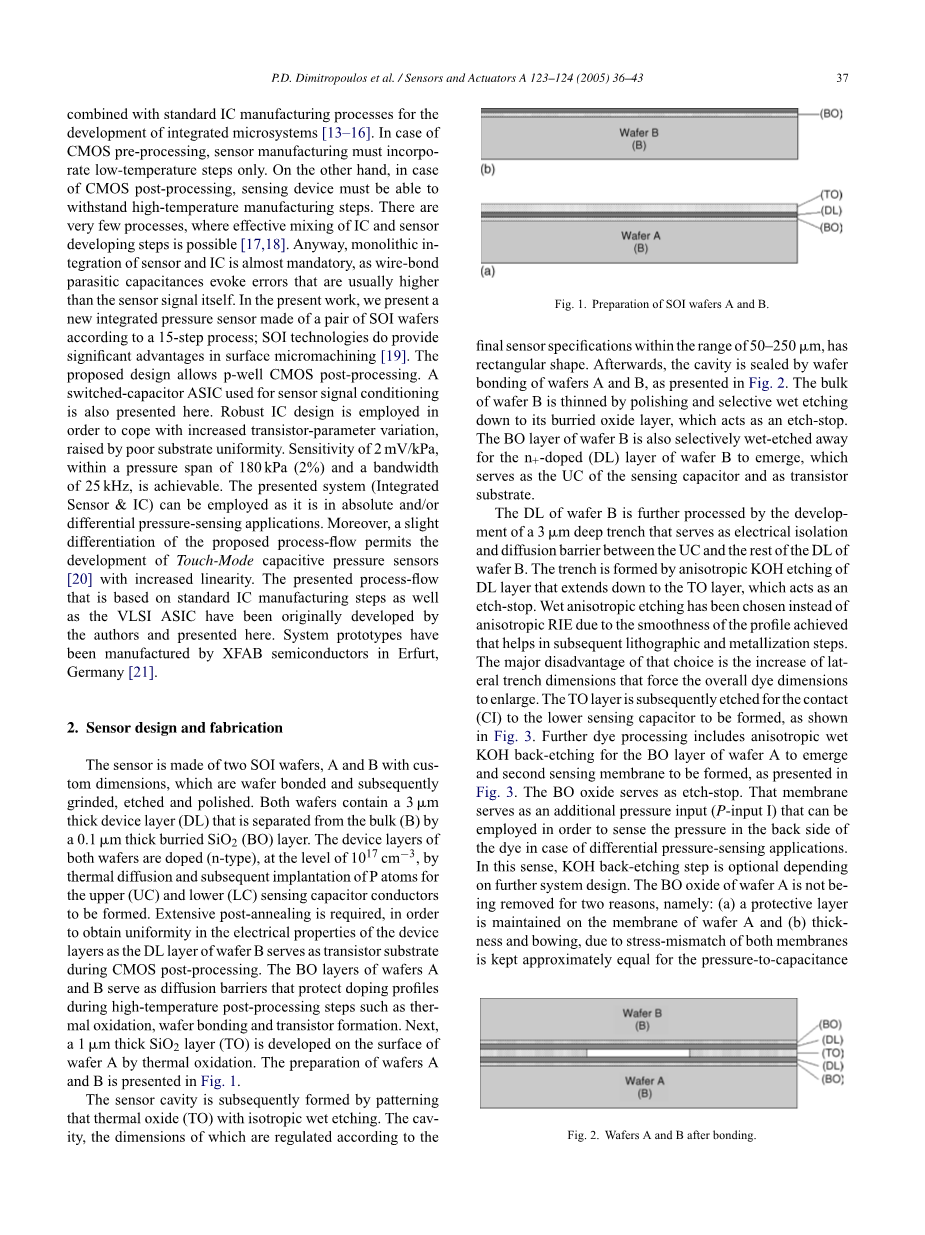

传感器腔体随后通过各向同性湿蚀刻图案化热氧化( TO )来形成。腔的尺寸根据最终传感器规格在50 - 250 m矩形范围内进行调整。之后,如图2所示,通过晶片A和B的晶片键合来密封空腔。晶片B的体积通过抛光和选择性湿蚀刻减薄至其去毛刺的氧化物层,这起到了蚀刻停止的作用。晶片B的BO层也被选择性地湿法蚀刻掉,使晶片B的n 掺杂( DL )层露出来,该层用作感测电容器的UC和晶体管衬底。

图2键合后的晶片A和B

晶片B的DL由3m深沟槽的发展进一步处理,该沟槽用作UC和剩余DL B之间的电隔离和扩散阻挡层。沟槽通过DL层的各向异性KOH蚀刻形成,该蚀刻向下延伸到TO层,起到蚀刻停止层的作用。湿各向异性蚀刻已经被选择来代替非共沸RIE,这是因为所获得的轮廓的平滑性有助于后续的光刻和金属化步骤。该选择的主要缺点是沟槽侧面尺寸的增加,这迫使整个染料尺寸增大。如图3所示,随后蚀刻TO层去形成与下部感测电容器的接触( CI )。进一步的染料处理包括对晶片A的BO层进行各向异性湿法KOH反蚀刻,以产生第二感测膜,如图3所示,氧化硼用作蚀刻终止剂。该膜作为额外的压力输入( P输入I )保存,在压差传感应用的情况下,可以使用它来检测染料背面的压力。从这个意义上说,KOH后蚀刻步骤是可选的,取决于进一步的系统设计。晶片A的氧化BO没有被去除由于两个原因,即: ( a )保持在晶片A的膜上的保护层和( b)厚度和弯曲,这是由于两个膜的应力失配,对于剩余的两个输入( P输入I和II )的压力-电容转换灵敏度来说,两个膜保持大致相等;在晶片B的膜上,在最后的工艺步骤中,通过PECVD沉积一层保护性SiN层。

图3工艺流程后的压力传感器

最后,在晶片B的DL层作为晶体管衬底的情况下,采用了标准的p阱CMOS工艺。井形成、晶体管开发、接触PI和PII的形成、金属化和钝化均遵循常规CMOS程序。然而,晶体管n -衬底的电特性的均匀性较差。为了克服这一困难,开发了一种特殊的模拟ASIC,其性能对晶体管参数变化相当稳定。为了清楚起见,在图4中给出了该设备的3D实体模型。

图4 压力传感器的三维模型:垂直切割

带有膜的传感器的校准数据,横向尺寸Dtimes;D,其中D= 200m,如图5所示。校准数据是借助CoventorWare工具的广泛有限元建模获得的。两个压力输入的灵敏度在P = 100 kPa时近似等于SP = part;C/part;Pasymp;1.32 fF/kPa,D= 200mand近似与spor;D4成比例,这与理论相符。D= 200m.时,最大可能压力为FSP = 200千帕,进一步的压力增加迫使膜接触。模拟ASIC的设计方式可以防止这种短路。在一个工艺中,厚度为0.1m的氧化物的替代物沉积在晶片B的DL层上,并且没有图案化。晶片A的TO层的厚度减小到0.5m.,后者的TO层被图案化以形成传感器腔,如前所述。以这种方式,正在开发一种触摸模式电容式压力传感器,该传感器在各种环境中显示出增加的线性度和抗干扰性的优点。

图5。具有矩形膜的传感器的校准数据,其中D= 200m: (a )电容变化对P输入I和II处施加的压力,以及( b )输入I和II膜的偏转。借助CoventorWare工具,通过广泛的有限元建模获得了数据。

图4

3 .模拟信号处理专用集成电路

在本项目中,最难处理的问题之一是模拟ASIC的设计,该设计旨在通过标准p阱CMOS工艺进行后期制造,其中晶片B的DL层用作晶体管n衬底。ASIC符合一系列允许其功能和传感电容器的重要规范,即: ( a )它必须启用差分和/或绝对压力传感能力,并在过压情况下提供短路保护,( b )它应该消耗尽可能低的功率,以实现无线传感应用;对于这种低压设计是强制性的,( c )它必须在延长的 50°至 150°C的范围内,( d )它应使用尽可能少的晶体管,以减小整体染料尺寸,( e )它必须补偿与传感电容器并联的寄生电容;寄生电容会引起与传感器信号一样大的误差, ( f )其性能必须尽可能少地依赖于由于晶体管衬底的不良电性能均匀性而引起的晶体管参数变化。

传感器信号由开关电容CMOS 由ASIC采样并预放大,该ASIC呈现在图6中 .ASIC是基于CMOS电荷转移放大器的,该放大器以共栅配置连接,以便利用MOS晶体管源极端中的低阻抗输入“可见”。只要晶体管的纵横比保持高于W/Lge;1,它们的尺寸是相等的,在ASIC性能中起着次要作用;设计中采用的纵横比为0.5。ASIC包含20个CMOS开关,由一对互补晶体管组成,如图7所示。互补设计很重要,因为开关电荷注入可能会产生重要误差。开关由两个不重叠的两相时钟信号控制,即: ( a) CP1和( b) CP2。这些信号的偶数和奇数相位分别用字母E和O相加来表示。开关相位序列如表1所示。

图6 预放大ASIC级

对于压差传感应用,电容器C4如图8(a )所示制造;它对施加在染料两侧的压力敏感( P输入I和II )。电容器C2和C3如图8(b )所示制造;它们对施加在传感器上侧的压力敏感( P输入II )。电容器C1和C5 - C8如图8(c )所示制造;它们对施加的压力不敏感。对于绝对感测应用,电容器C4也如图8(c )所示制造。在图8中,为了简单起见,省略了接触和沟槽。所有电容器具有相同的零压力电容,即C0 asymp;5 pF。电容器C7和C8以及四个相应的开关构成一个采样保持电路,该电路连接到一对模拟电流传送器上,这一对模拟电流传送器在其他地方出现。在目前的输送机设计过程中,为了在低压应用情况下最大限度地提高其动态范围,已经非常小心。分别用VDD和VSS表示的正电源电压和负电源电压设置为- VSS = VDD = 1.6V。

图7 开关

晶体管栅极端子连接到模拟地。以这种方式,晶体管大致起到它们的源极端电压控制开关的作用。PMOS晶体管只要其源极端电压高于VSP ge;VTP (其中VTP表示其阈值电压),就会导通。类似地,只要VSNle;VTN,nMOS晶体管就导通。在阶段0期间,电容器C1 - C6被重置,这意味着它们的电荷被设置为CiVDD值。在阶段1期间,电容器C1 - C4被预充电。MOS晶体管传导预充电电容C1 - C4的电流,直到PMOS和NMOS源极端的电压分别变为VTP和VTN。所需的电流在阶段1期间,电容器预充电通过晶体管漏极端子馈送到模拟地。在阶段2结束时,电容器C1 - C6充满电。它们连接到PMOS和PMO源极端子的导体的电压分别保持在VTP和VTN,而它们连接到电源的导体的电压分别变为VDD和VSS。在阶段2期间,晶体管漏极端子连接到C5和C6电容器。这样,电荷Q5和Q6分别被送到这些电容器,迫使它们的电压升高,分别用V5和V6表示。

Q1(nTs) = C0VDD

Q2(nTs)=(C0 C2(nTs))VDD (1a)

Q3(nTs) = (C0 C3(nTs))(minus;VSS) = (C0 C3(nTs))VDD

Q4(nTs)=(C0 C4(nTs))(minus;VSS)=(C0 C4(nTs))VDD (1b)

Q5(nTs) = Q1(nTs) minus; Q3(nTs) = C3(nTs)VDD

Q6(nTs)=Q2(nTs)minus;Q4(nTs)=(C2(nTs)minus;C4(nTs))VDD (1c)

V5(nTs) = Q5(nTs)/2C0

V6(nTs)=Q6(nTs)/2C0 (2a)

V7(nTs) = 1/2V7((n minus; 1)Ts) Q5(nTs)/2C0

V8(nTs)=1/2V8((nminus;1)Ts) Q6(nTs)/2C0 (2b)

V0(nTs)=V7(nTs)minus;V8(nTs)=1/2V0[(nminus;1)Ts] [C4(nTs) minus; C2(nTs) minus; C3(nTs)]/2C0*VDD (2c)

电荷Qi(t )和电压Vi(t )在等式中计算。( 1 )和( 2 ),分别地表示相应的电容器。电压V7和V8减法由电流传送器执行。ASIC输出信号V0(t )是频率fs =1/Ts = 50 kHz的离散时间脉冲幅度调制( PAM )波形,这是传感器采样率以及CP1和CP2时钟信号的频率。电容变化C2和C3取决于施加在芯片上侧的压力Pii ( P输入II ),而电容变化C4取决于施加在芯片两侧的压力Pi Pii ( P输入I和II )。 ( 2 )显示采样保持子电路(电容器C7和C8 )与电容器组合。C5和C6形成截止频率fLP = 0.5 fs = 2

全文共11748字,剩余内容已隐藏,支付完成后下载完整资料

资料编号:[519]