英语原文共 14 页,剩余内容已隐藏,支付完成后下载完整资料

交错式多相dc-dc转换器中电感耦合效应的分析和验证

摘要—交错式多相同步降压转换器通常用于为计算机CPU,GPU和内存供电,以满足增加处理器的负载电流和快速电流摆率的需求。 本文报告并解释了空间受限的典型商用多相应用中分立电感器之间的不良耦合。 本文推导了多相转换器中常用的单匝和多匝铁氧体磁芯电感的耦合系数方程,并通过麦克斯韦静态仿真进行了验证。 耦合效应对电感器电流波形的影响已通过麦克斯韦瞬变仿真得到证实,并通过实验得到了证实。 该分析为减轻多相转换器的耦合效应提供了有用的工具,可避免电感器过早饱和以及相之间的干扰。 提供了设计指南和建议,以最大程度地减少多相转换器中的有害耦合效应。

关键词-耦合,DC-DC电源转换器,电感,电感器,磁芯,磁通密度,数学模型,仿真,开关转换器。

Ⅰ、引言

下一代高性能服务器,台式机,存储和通信系统中央处理器(CPU),图形处理器(GPU)和双倍数据速率(DDR)存储器对高达300A负载电流的电源管理要求提出了越来越高的要求 在大约1 V的低电压下,电流压摆率高达300 A /mu;s[1]。 这些系统的关键要求是非常高的效率,快速的负载瞬态响应,减小的空间和低成本。 为了满足这些要求,交错多相同步降压转换器已用于为大多数CPU,GPU和DDR存储器供电[2] – [6]。

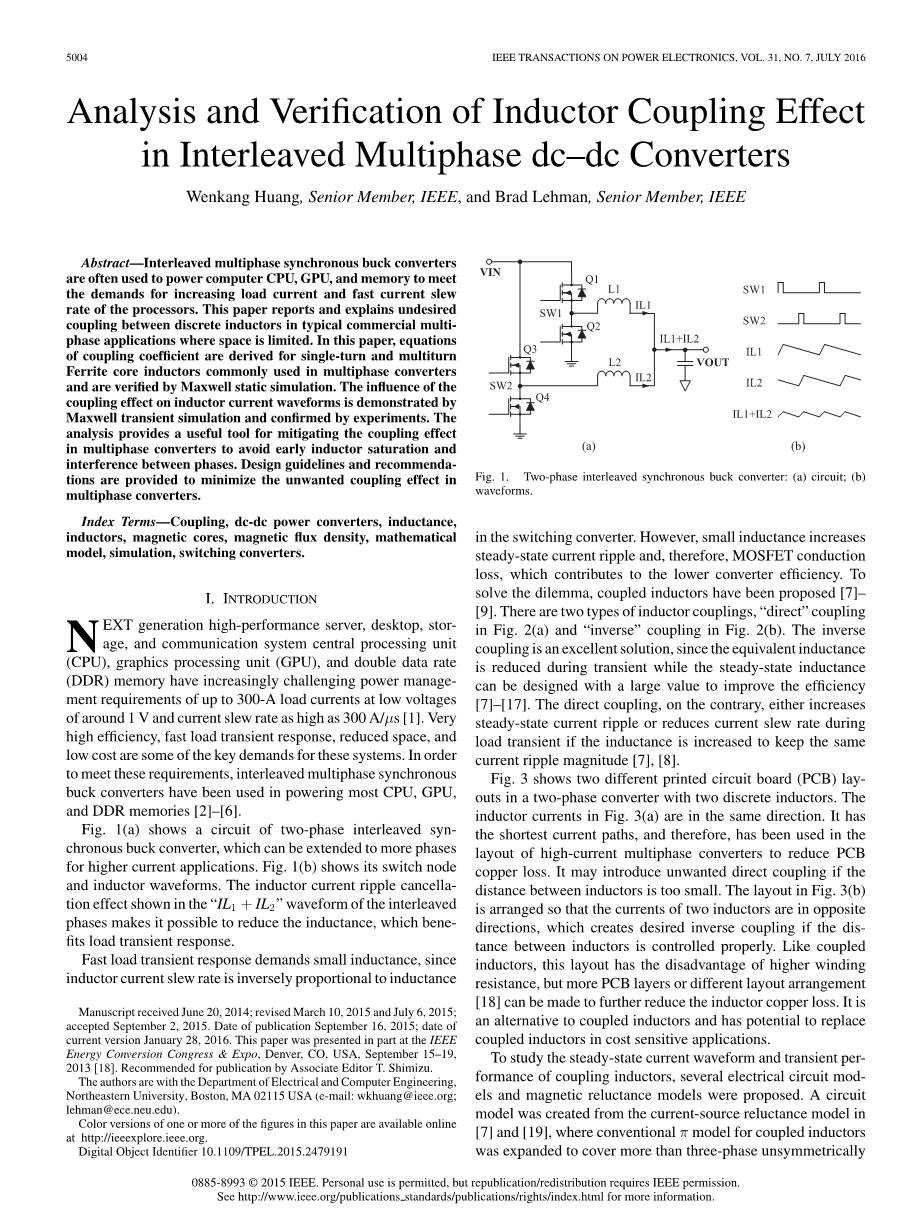

图1(a)显示了两相交错式同步降压转换器的电路,该电路可以扩展到更多相以用于更高电流的应用。 图1(b)显示了其开关节点和电感器波形。 交错相的“ IL1 IL2”波形中显示的电感器电流纹波消除效果可以减小电感,这有利于负载瞬态响应。

图1.两相交错式同步降压转换器:(a)电路; (b)波形。

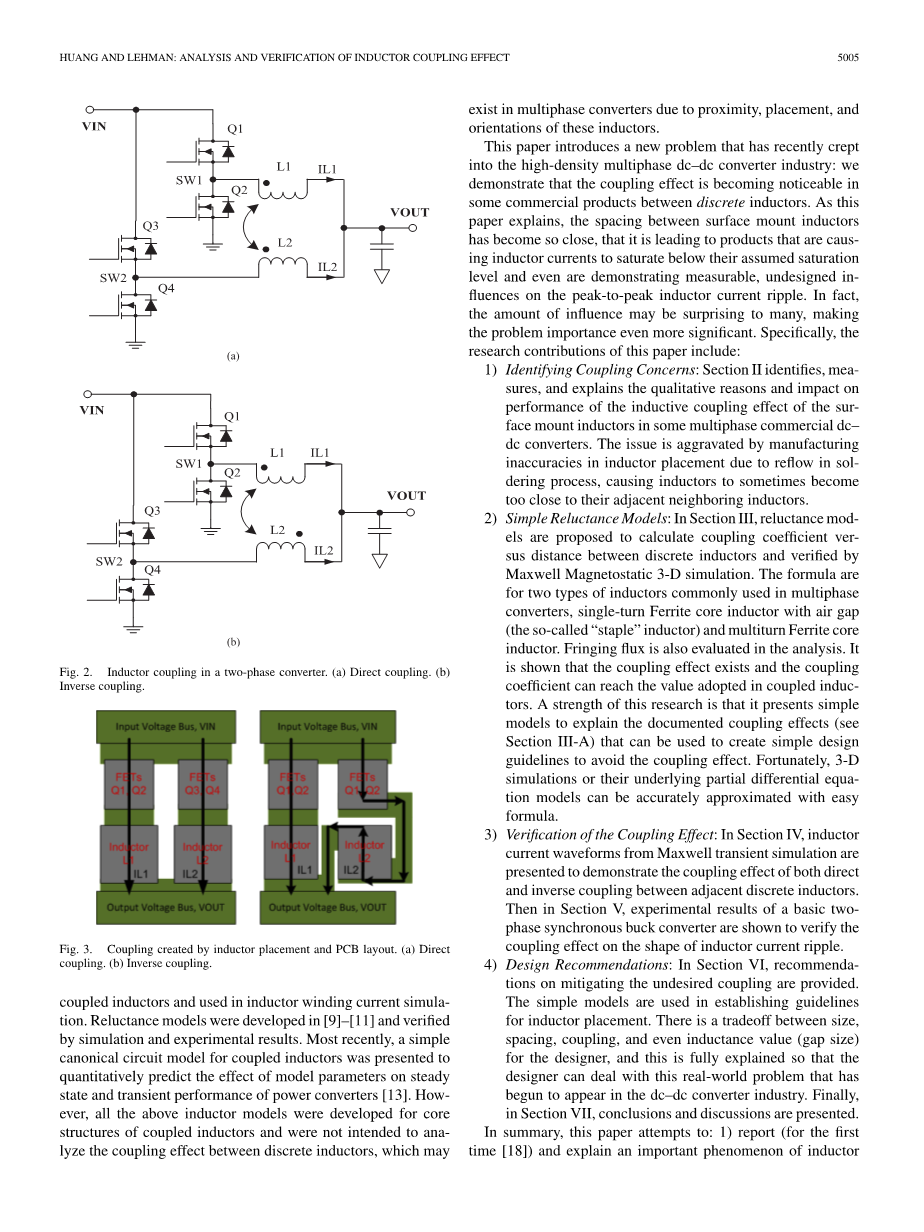

快速的负载瞬态响应需要较小的电感,因为电感电流的摆率与开关转换器中的电感成反比。但是,较小的电感会增加稳态电流纹波,因此会增加MOSFET的导通损耗,从而导致转换器效率降低。 为了解决这个难题,已经提出了耦合电感器[7] – [9]。 电感耦合有两种类型,图2(a)中的“直接”耦合和图2(b)中的“反”耦合。 反向耦合是一个很好的解决方案,因为在瞬态过程中等效电感会减小,而稳态电感可以设计为较大的值以提高效率[7] – [17]。 相反,如果增加电感以保持相同的电流纹波幅度,则直接耦合会在负载瞬变期间增加稳态电流纹波或降低电流压摆率[7],[8]。

图2.两相转换器中的电感耦合。 (a)直接耦合。 (b)逆耦合。

图3显示了具有两个分立电感的两相转换器中的两种不同的印刷电路板(PCB)布局。 图3(a)中的电感电流方向相同。 它的电流路径最短,因此已被用于大电流多相转换器的布局中,以减少PCB的铜损。 如果电感器之间的距离太小,可能会引入有害的直接耦合。 图3(b)中的布局被布置成使得两个电感器的电流处于相反的方向,如果适当地控制电感器之间的距离,则这将产生期望的逆耦合。 像耦合电感一样,这种布局的缺点是绕组电阻较高,但是可以制作更多的PCB层或使用不同的布局布置[18],以进一步减少电感的铜损。 它是耦合电感器的替代品,在成本敏感型应用中有潜力取代耦合电感器。

图3.电感放置和PCB布局产生的耦合。 (a)直接耦合。 (b)逆耦合。

为了研究耦合电感的稳态电流波形和瞬态性能,提出了几种电路模型和磁阻模型。 从文献[7]和[19]中的电流源磁阻模型创建了一个电路模型,其中将用于耦合电感器的常规pi;模型扩展到涵盖超过三相非对称耦合电感器,并用于电感器绕组电流仿真。 在[9] – [11]中进行了开发,并通过仿真和实验结果进行了验证。 最近,提出了一种用于耦合电感的简单规范电路模型,以定量预测模型参数对功率转换器的稳态和瞬态性能的影响[13]。 但是,上述所有电感器模型都是针对耦合电感器的核心结构开发的,并不旨在分析离散电感器之间的耦合效应,由于这些电感器的接近度,位置和方向,它们可能存在于多相转换器中。

本文介绍了一个新问题,该问题最近已进入高密度多相DC-DC转换器行业:我们证明,在某些商用产品中,分立电感器之间的耦合效应变得越来越明显。 正如本文所解释的,表面贴装电感器之间的间距已变得如此之近,以至于导致产品导致电感器电流饱和到其假定的饱和水平以下,甚至对峰峰值电感器表现出可测量的,未经设计的影响 电流纹波。 实际上,影响力之大可能令许多人感到惊讶,从而使问题的重要性更加显着。 具体来说,本文的研究贡献包括:

- 识别耦合问题:第二部分确定,测量和解释了一些多相商用dc-dc转换器中表面安装电感器的电感性耦合性能的定性原因及其影响。 由于焊接过程中的回流焊导致的电感器位置制造不准确,使该问题更加严重,从而导致电感器有时变得太靠近其相邻的相邻电感器。

- 简单的磁阻模型:在第三节中,提出了磁阻模型来计算耦合系数与分立电感器之间的距离,并通过Maxwell静磁3-D仿真进行了验证。 该公式针对多相转换器中常用的两种类型的电感:带气隙的单匝铁氧体磁芯电感器(所谓的“装订”电感器)和多匝铁氧体磁芯电感器。 分析中还评估了边缘助焊剂。 结果表明存在耦合效应,耦合系数可以达到耦合电感所采用的值。本研究的优势在于,它提供了简单的模型来解释已证明的耦合效应(请参阅第III-A节),可用于 创建简单的设计指南以避免耦合效应。 幸运的是,可以通过简单的公式精确地逼近3-D仿真或其基本的偏微分方程模型。

- 耦合效应的验证:在第四部分中,通过麦克斯韦瞬态仿真给出了电感器电流波形,以证明相邻分立电感器之间直接耦合和反向耦合的耦合效果。然后在第五部分中,基本的两相同步降压转换器的实验结果为 如图所示,以验证耦合对电感电流纹波形状的影响。

- 设计建议:在第六节中,提供了有关减少不希望有的耦合的建议。简单模型用于建立电感器放置准则。 设计人员需要在尺寸,间距,耦合和甚至电感值(间隙尺寸)之间进行权衡,这已得到充分说明,以便设计人员可以解决已在dc-dc中开始出现的这个实际问题。 转炉行业。 最后,在第七节中,提出了结论和讨论。

总而言之,本文试图:1)首次报告[18],并解释电感耦合的一种重要现象,这种现象已开始影响某些商用多相转换器的性能; 2)创建足够准确和简单的模型,以供设计人员用来描述新发现的电感耦合; 3)提出可用来减轻可能发生的意外感应耦合效应的设计规则; 4)使用商业产品和实验室规模的原型通过实验验证结果。

Ⅱ、离散电感器之间不需要的耦合问题

由于无源组件的技术发展和无源器件的尺寸减小速度要比硅器件慢,因此电感器是功率开关转换器中最大的组件,因此,它们占据了转换器的整体尺寸。 如图3所示,电感器比MOSFET宽,因此电感器而不是MOSFET的间距是减小转换器尺寸的限制因素,尤其是在刀片服务器等空间受限的应用中。 在某些设计中,情况变得更糟,在这些设计中,在路由系统信号总线后只剩下一小部分空间用于功率转换器。 另一个例子来自下一代英特尔处理器,该处理器需要用于CPU的较小宽度的多相转换器,以便DDR可以更靠近CPU放置,以在它们之间实现更高的通信速度。 电感器之间的距离必须进一步减小,以使转换器适合较小的空间。

由于在回流过程中难以控制电感器之间的距离,因此表面贴装焊接加剧了该问题。 电感器可能会在回流期间由于其漂浮在熔融焊料上的能力而移位,但是漂浮在熔融焊料表面上的电感器受到限制,这会导致电感器未对准。 根本原因是电感器比其他组件重,并且无铅焊料的流动能力受到限制,这已在近年来引入电子产品制造。

图4(a),(b)和(c)显示了我们为该研究项目测试的十个商用四相转换器板中的三个,组装后每个电感器之间的间距都不同。 相邻电感之间的预期间距约为0.65 mm,而没有实现设计人员的潜在耦合效果,而实际间距是通过塞尺测量的,如表I所示。图4(a)中的电感间距对应于板#1 比设计的要宽。 图4(b)示出了板#3,其代表典型的组装板。 图4(c)显示由于电感器的未对准,导致板#5中的间距更加不均匀,其中之一甚至小于0.2 mm。

图4.商用多相转换器中回流后的电感器未对准。 (a)董事会#1。 (b)第3局。 (c)第5局。 (d)刀片服务器主板#1。 (e)刀片服务器主板2。

在具有多相控制器的五块板上进行了电感器饱和测试,这些控制器在稳态和瞬态期间保持相位交错。 测试条件如表I所示。由于电感器饱和电流随温度变化,因此在所有电路板的测试中均保持相同的电感器温度,以达到一致的结果。 对于每个测试的电路板,我们遵循以下步骤:施加直流电流负载,以5 A /mu;s的固定压摆率向转换器添加相同的120A步进电流,并增加直流负载,直到电感饱和被正确捕获 在120 A负载阶跃之后。

表Ⅰ三相转换器中电感的距离和饱和电流

示波器探头直接连接到电感器L4的VOUT侧,以便于检测电感器电流尖峰。 没有电感饱和的转换器输出电压的正常波形如图5(a)所示。 当电感器饱和在重负载下发生时,电感器电流斜率会增加,这会导致在相同占空比下出现更高的峰值电流。 如图5(b)所示,较高的电流斜率和幅值会在输出电压上产生尖峰,用于触发示波器并捕获电感器饱和事件。 在120A负载瞬态响应测试期间,开关频率略有变化,但多相控制器保持了相位交错关系。

图5.转换器输出电压波形 (a)正常运行。 (b)电感饱和。

每块板的总电感饱和电流记录在表I中,不同电感温度下每相的饱和电流如图6所示。每块板使用相同的电感磁芯和相同的值。 由于电感之间有足够的间距,因此板#1具有最高的饱和电流。 #2至#4电路板的饱和电流较低,由于间距的减小,它从#2至#3至#4略有减小。#5电路板是电路板组装中最差的情况,并表现出约10 A /的下降 相与#1板相比饱和电流中的相位差。 这表明由于组件中电感未对准的余量和电感机械尺寸(宽度)不足,导致各相之间电感直接耦合。 如第V节所示,直接耦合会改变电感器电流的形状并增加峰值纹波电流,这会导致电感器过早饱和并危害转换器中的MOSFET。

图6.商用多相转换器中每相的电感器饱和电流。

在没有意识到电感器耦合的严重性的情况下,某些商用产品的设计没有足够的裕量来保证电感器间距。 图4(d)和(e)所示的刀片服务器主板是其中两个示例。 表II中显示了用于CPU的四相转换器中电感之间的间距,最小间距为0.279 mm。 为了最小化或消除电感之间的直接耦合,必须在转换器设计中保持额外的间距以确保足够的间隙余量,这浪费了主板上的宝贵面积,并且在某些紧凑型设计(例如刀片服务器)中不可行。

表Ⅱ商业主板上的感应器之间的距离

Ⅲ、电感耦合效应分析与验证

在本节中,我们导出简化的模型来描述第二节中注意到的耦合效应。 将结果与高保真3D仿真模型进行比较,并证明是准确的。

- 单匝铁氧体磁芯电感

在多相转换器中使用的三种类型的电感器中,单匝“定型”铁氧体磁芯电感器因其较低的直流电阻和较大的饱和电流而在服务器应用的转换器中最受欢迎。 电感被限制在数百个毫微亨里,但是由于电感较小而产生的较大电流纹波可通过相交织或较高的开关频率来补偿。

单匝型电感器在两相转换器中的放置如图7所示,其中“ d”是两个电感器之间的距离,“ g”表示电感器中的气隙。 为了简化一系列电感器的制造过程,在为不同的电感器值调整气隙的同时,两个磁芯的尺寸应保持相同。

图7.单匝铁氧体磁芯电感器。

图8示出了两相转换器中的分立电感器L1和L2的芯结构和等效磁阻电路。 如图8(a)所示,每个电感器都有一个单匝绕组。 实线表示从一个电感器的绕组耦合到另一电感器的绕组的磁通,而虚线表示未耦合的磁通。 图8(b)显示了等效磁阻电路,其中zeta;1和zeta;2是磁通势(MMF)源,而R1,R2,R3和R4是磁阻。

图8.两个单匝分立电感器的磁阻模型。 (a)铁心结构和联轴器,正视图。 (b)等效磁阻电路。 (c)磁路尺寸,正视图。 (d)横截面尺寸,顶视图。 (e)横截面尺寸,侧视图。

自感L,耦合电感M和耦合系数alpha;的方程式分别用(1),(2)和(3)表示,其中N是匝数,对于“钉书钉”型电感器,N = 1 。

- 中的磁阻Rd1和(7)中的磁阻Rd2由两个分立电感器之间的距离产生,而(6)和(7)中的磁路磁阻与磁路l3或l4的平均长度成正比并成反比 分别到截面A2a或A2b。 mu;r是铁氧体磁心的相对磁导率,mu;0是真空磁导率。磁阻R1和R2由气隙磁阻Rg和磁路磁阻组成,它们与磁路l1和l2的平均长度成比例(= l2a l2b l2c 如图8(c)所示,由(4)和(5)定义。 A1,A2a,A2b和A2c是分别对应于l1,l2a,l2b和l2c的电感器的横截面,如图8(d)和(e)所示。 (6)中的间隙磁阻Rd1和(7)中的磁阻Rd2由两个分立电感器之间的距离产生,而(6)和(7)中的磁路磁阻与磁路l3或l4的平均长度成正比, 分别与横截面A2a或A2b成反比。 mu;r是铁氧体磁芯的相对磁导率,mu;0是真空磁导率

可以包括气隙的边缘通量,但由于它的影响最小,因此已被忽略,这将在III-B节中进一步说明。 当不考虑气隙的边缘通量时,(4)-(7)中的气隙磁阻Rg,Rd1和Rd2与气隙g或d成正比,如(8)所示。

通过使用磁阻模型的(3)–(8),无需考虑边缘磁通,可以针对不同的电感器值计算耦合系数alpha;与距离d的关系,如图9(a)所示。150- 计算中使用的nH电感在表III中列出。 耦合系数随着电感值的降低或气隙的增大而增加。 当d = 0mm时,即两个电感器放在一起时,耦合系数达到最大值

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[237716],资料为PDF文档或Word文档,PDF文档可免费转换为Word