英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

基于仲裁的物理不可控制功能在FPGA上的安全性增强

【摘要】为了减少仲裁者的亚稳性和偏见引起的物理不可克隆函数(PUF)响应不稳定和不平衡,本文在不平衡D触发器(DFF)的基础上,使用改进的平衡DFF来减少响应输出和输出中的偏差。通过串联采用两个平衡DFF,可以提高PUF的安全性。实验结果表明,两个级联的平衡DFF提高了DFF的稳定性,并且两个平衡DFF的输出更加可靠。输出的熵固定为98.7%。

关键词:物理不可克隆函数;压稳性;平衡D触发器;现场可编程门阵列(FPGA);安全性

0 引言

物理不可克隆函数(PUF)是利用制造过程的随机可变性来识别每个设备的物理实体[1]。它的行为易于评估,但难以预测。它的行为易于评估,但难以预测。 PUF因其功耗低且设计简单,在许多安全应用程序中有着重要作用,例如密钥生成[2],身份验证[3],对象跟踪[4]和知识产权(IP)保护[5]。设计PUF的方法很多,例如环形振荡器(RO)PUF,静态随机存取存储器(SRAM)PUF和蝶形PUF [6-8]等。为了表征每个器件,在RO PUF中使用了振荡频率,在SRAM PUF和Butterfly PUF中使用了存储单元的初始值的测量[9]。这些PUF比基于仲裁器的PUF更为复杂,后者可以简化并缩小电路设计。这种基于仲裁器的PUF主要利用产品固有的物理指纹作为其自己的唯一标识[10]。例如,身份可用于加密密钥生成[11]。为了保证PUF输出的鲁棒性,本文提出了模糊提取器以确保生成的两个密钥完全相同[12]。

基于仲裁者的PUF由Gassen等人[13]首次提出。它基于两条并行路径之间的相对延迟差异。但是,仲裁器PUF一直受到安全威胁,例如建模攻击,亚稳定性和不平衡结果[1]。 为了防止模型攻击,Suh等人[14]提出了一种方法,通过对多个PUF电路输出进行XOR或使用PUF输出作为多路复用器的控制信号来解决该问题。关于PUF结构研究的文献很多,但是对于如何改善亚稳性问题的研究很少。Majzoobi等人[15]提出了一种使用可编程延迟线的基于仲裁器的现场可编程门阵列(FPGA)PUF,以提高DFF的亚稳定性,即采用移位寄存器和多数表决逻辑来减少响应输出的不稳定性。Capovilla等[1]利用平衡的SR锁存器来改善DFF的偏差评估。但是,SR锁存器对毛刺脉冲很敏感,这可能会导致错误的输出。

为了提高PUF响应的可变性,我们提出了一个平衡DFF以平衡PUF响应中0s和1s的分布,并且我们使用两个串联的平衡DFF进一步减轻了仲裁者的亚稳态,这比多数表决更为简单和节省资源模块。为简单起见,除了多数表决模块和移位寄存器之外,基于仲裁器的PUF我们采用了参考文献的方法[15]。通过提高响应可变性和稳定性,可以提高基于仲裁器的PUF的安全性。

本文的贡献如下:

- 基于非平衡DFF提出了平衡DFF,以减少输出结果中的偏差,并且输出具有较高的熵值。

- 通过使用两个级联的平衡DFF,减少了由于DFF的亚稳定性引起的响应的不稳定性。

- 基于FPGA进行了实验评估,以验证平衡DFF与不平衡DFF的优势。

本文的其余部分安排如下:第1节介绍了基于仲裁的PUF及其相关工作的初步知识。第2节提供了增强PUF安全性的措施。 在第3节中,介绍了度量参数,实验结果和详细分析。 最后,结论和相应的未来工作在第4节中给出。

0 初步工作

1.1 PUF的应用架构

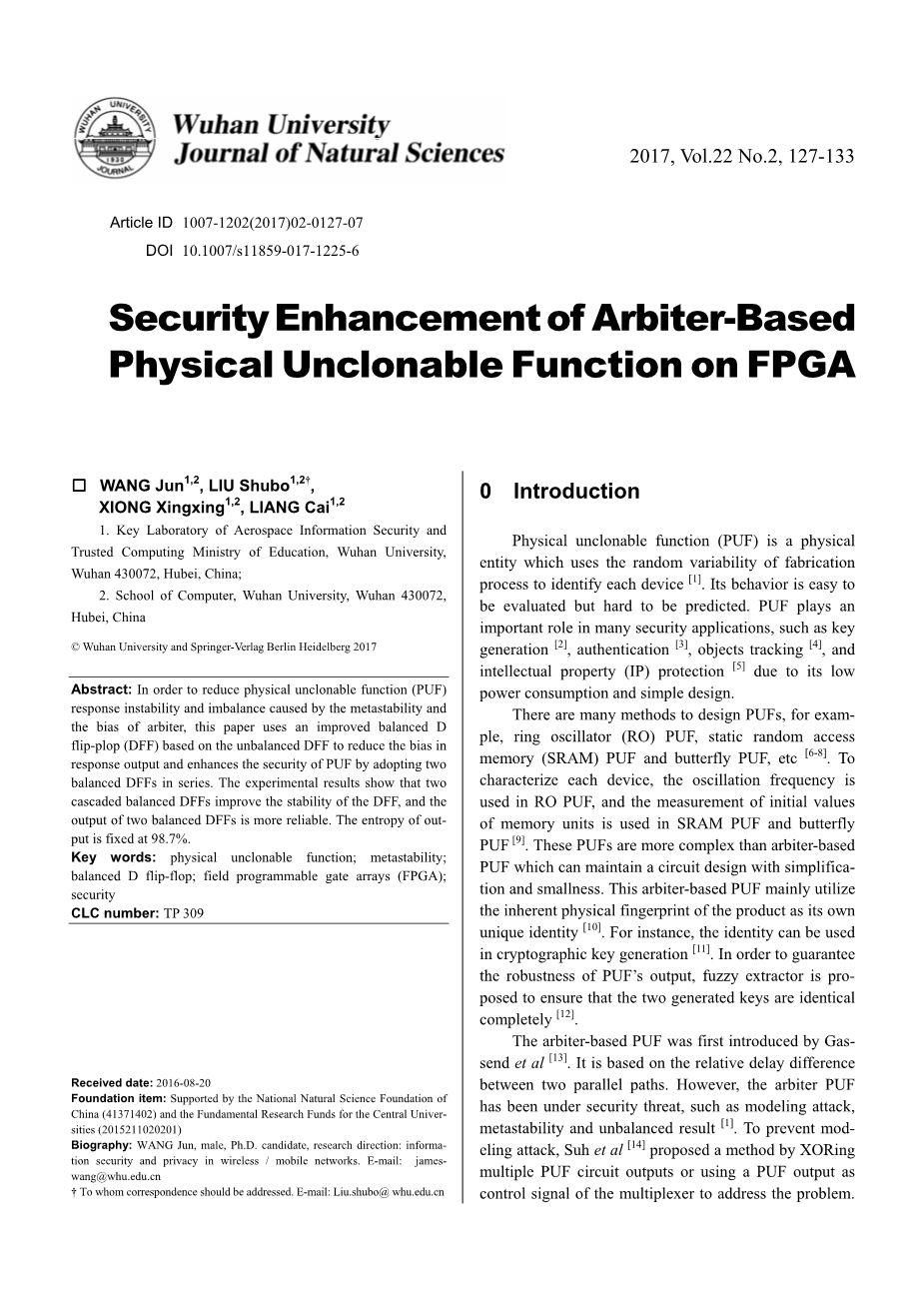

PUF利用硅器件的不可克隆固有的制造变化,以产生可测量的挑战响应对(CRP)[16]。CRP的独特性和不可预测性确保了PUF的应用程序安全性。PUF的应用架构如图1所示。

图1 PUF的应用架构

利用PUF生成的易失性存储器中的加密密钥,攻击者将无法通过物理入侵获得秘密密钥。使用PUF,密钥状态更加安全,因为仅在需要时才生成CRP [9]。与密钥生成类似,身份验证具有高度的安全性。它可以利用机器学习来训练PUF模型以进行应用[17,18]。与不存储CRP的方法相比,不存储CRP的存储技术[14]不利于应用程序的扩展,只是一种常规方法,它直接将CRP保存在非易失性存储器或背景数据库中。如果应用程序需要一个随机CRP将被选中。 PUF为模糊提取器和机器学习提供了底层支持。 PUF越稳定,应用程序就越安全。

1.2 基于仲裁器的PUF

PUF受到了广泛关注,其定义如下。

定义1 PUF是不可逆的功能,可以将挑战映射到响应并利用物理设备的制造变化来获得唯一的CRP [13]。PUF有许多优点。一方面,通过功能可以在短时间内以简单的电路结构轻松生成CRP。另一方面,很难窃取CRP的值,因为任何物理入侵都会损坏设备的正常电路结构。 特别是,不可能生产两个相同的PUF,因为它们的电路特性超出了制造过程的控制范围[13]。

图2说明了基于多路复用器的硅PUF延迟电路,该电路具有两条具有相同布局的延迟路径[14]。 电路的输入是多位质询c,输出是由两个并行路径之间的相对延迟差确定的1位响应。精确的信号路径由控制多路复用器中脉冲信号的精确路径的多位挑战 决定。换句话说,如果挑战ci的值为零,则将选择上,下路径。否则,两条路径切换位置,如图3所示。

图2仲裁器PUF延迟电路

图3多路复用器电路

在n个多路复用器的末尾,通常由DFF实现的仲裁器首先判断哪个信号到达。 如果首先到达锁存器数据输入的信号,则DFF的输出为零;否则,DFF的输出为零。 否则,DFF的输出为1(如图4所示)。

图4仲裁器的输出

仲裁器的输出可以通过以下公式计算。

(1)

其中,是一个向量,由脉冲信号在顶部和底部路径中的延迟引起,是一个转换挑战向量,其中[16,19]。

尤其是,如果在clk和D处的两个路径信号之间的延迟小于仲裁器的设置和保持时间,则将出现亚稳态,并且响应将是随机且不可预测的[1]。 亚稳是一种不良现象,会导致数字电路故障并降低数据的可靠性[20]。 DFF中亚稳态的行为如图5所示。

图5 DFF中的亚稳定性

DFF建立时间tsu是输入信号保持稳定的最短时间; DFF保持时间是信号的保持时间,在此期间不保持过渡; tco是关于输出的时钟转换的延迟时间。 如果DFF的输入信号不满足tsu和th或延迟时间超过tco [21,22],则会发生亚稳。 当发生亚稳态时,PUF的输出是不确定的,即,输出值可能为“ 1”或“ 0” [23]。

1.3基于仲裁器的PUF的相关工作

为了减少由不对称引起的不平衡延迟偏差,仲裁器PUF电路必须确保仅由制造偏差产生延迟差,并且在PUF布局中顶部和底部路径完全对称[15,24]。

为了改善平衡并达到雪崩准则,Majzoobi等人[16]和Rostami等人[25]使用4-XOR混合PUF来使输出跃迁的概率接近理想值0.5,因为两个独立的线性 异或混合PUF可以获得更好的统计属性。 注意,将4-XOR混合的PUF的错误概率估计为19%[26]。

FPGA上的路由受到其互连结构的约束和不确定[27],因此顶部和底部路径之间的完美对称在物理上几乎是不可行的。为了解决信号路由中的不对称性,Majzoobi等人[15]采用了可编程延迟线(PDL)来调整和校准延迟偏置。查找表的信号传输路径由输入值控制,因此,通过更改输入的值,信号可以通过不同的路径传播。换句话说,可以获得各种延迟差异。将K个调谐块插入路径的顶部和底部,以调谐或消除由信号路由不对称引起的不平衡差异(延迟偏差)[15]。

典型DFF的内部路径不平衡,因此这种不平衡结构与不可避免地会产生偏见。Capovilla等人[1]提出了一种平衡SR锁存器,以提高基于仲裁器的PUF的统计可变性,因为平衡SR锁存器是对称电路。

2增强PUF安全性的措施

2.1平衡DFF

仲裁器可以判断PUF电路末端的输出值。如果仲裁器的内部逻辑路径具有对称结构,则它们将运行良好并且几乎具有相同的路径延迟。否则,将在一条路径中发生有偏差的延迟。

仲裁器的逻辑结构通常采用典型的DFF [28,29],这可能会导致评估不均衡。 为了在逻辑上和物理上保持PUF的对称性,提出了平衡的DFF,其内部结构如图6所示。

图6平衡DFF

2.2改进的PUF

仲裁器的内部路径应具有相同的布局,并且有相同的从输入到输出的延迟[1]。因此平衡DFF将改善不均等的延迟偏置。如图6右上角所示,典型DFF的输入信号连接到不同的端口“X”和“Y”,即标有绿色的端口。 平衡DFF的输入信号连接到相同的端口“X”,该端口以红色线标出。

图7显示了改进的基于仲裁器的PUF电路的逻辑结构,该电路由三个模块组成:延迟链,调整链和级联的两个平衡DFF。除了连接前者中基于PDL的开关的选择器信号和分离后者中的选择器信号之外,延迟链与调整链的结构相同。

图7改进的基于仲裁器的PUF结构

电路的平均故障间隔时间(MTBF)用于评估亚稳定性,MTBF的定义如下[21]:

(2)

其中tr是亚稳态解析所允许的预定时间,Fc和Fd分别是时钟和数据的跃迁频率,Tw是有关可测量时间窗口的参数,而tau;是解析时间常数。 在级联的两个平衡DFF中,MTBF随着tr的增加而变大。

FPGA提供了可重复编程的互连模块的通用基板。FPGA的灵活性程序和敏灵活开发性使其在许多应用中得到广泛使用[15]。

给定用于改善电路的输入信号脉冲,该信号将通过两条平行路径,从而确保两条路径尽可能具有相同的电路延迟。由于其固有特性,信号将在PUF末尾到达不同的时间,然后生成PUF输出。

3实验

3.1参数指标

如果PUF响应的熵足够高,则PUF将同时捕获唯一性和不可预测性[30]。 我们使用熵检验来估计PUF响应的偏差,熵的定义如下。

定义2给定一个随机变量xi,p(xi)是xi的输出概率,则熵由下式给出

(3)

香农熵是一种合适的度量参数,用于测试二进制序列的偏差[31]。 例如,给定二进制序列“01011010”,二进制序列的熵为1。

3.2实验环境

我们在Altera FPGA板上进行了实验,该板在工业应用中具有许多优势,例如低功耗和小体积[27,32]。 FPGA的类型为EP1C3T100,具有100个引脚。 FPGA板如图8所示。

图8 FPGA板

开发工具是Quartus 8.0,设计文件是框图/原理图文件,分析工具是SignalTap Logic Analyzer,可以监视和采样数据。

Tektronix TDS 1012的采样率为1GS/s,带宽为100 MHz。实验在FPGA上进行,然后计算机通过联合测试行动组(JTAG)获得输出结果的反馈并显示实验结果。实验参数见表1。

|

Item |

Parameter value |

|

CPU |

Intel Core i5 |

|

RAM |

4.00GB |

|

Oscilloscope |

Tektronix TDS 1012 |

|

Signal generator |

Gwinstek |

|

Total memory bits |

59904 |

表1实验参数

3.3实验数据

二进制响应的熵如图9所示,它显示了响应中输出值“1”和“0”的偏差。

我们使用7种不同的二元响应进行了实验。 根据输出结果计算响应的熵。

图9 64位响应的熵分布

从图9可以看出,典型DFF的响应熵是不稳定的,并且小于或等于平衡DFF。 我们推断,改进的级联DFF的响应稳定性和可变性优于典型DFF。

图10(a)显示了Tektronix TDS 1012的亚稳输出图。如果发生亚稳,DFF的输出将不确定。输出的不确定性增加了

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[236484],资料为PDF文档或Word文档,PDF文档可免费转换为Word