英语原文共 11 页,剩余内容已隐藏,支付完成后下载完整资料

A Reconfigurable Platform for Magnetic Resonance Data Acquisition and Processing

一种可重构的磁共振数据采集和处理平台

摘要:磁共振成像(MRI)在过去几十年的发展中呈现出一个趋势,即使用越来越多的阵列线圈和越来越多的传感器。通过将数据采集装置靠近线圈,解决了相关的布线和安全问题。然而,随着射频(RF)信道数量的增加和更高的采集脉宽,数据量也在增长,这对吞吐量和数据处理提出了挑战。当它成为一种限制因素时,前期的压缩和预处理就变得越来越重要。此外,当传感器传输不同的数据时,往往会降低处理运行时更新扫描仪的操作速度。为了解决这些挑战,我们建议使用一个定制的接口和实时处理资源的应用程序来过渡到可重构硬件。我们提出了一个基于系统芯片(SoC)的集成解决方案,为平台提供了足够的吞吐量和基于硬件的并行处理能力。该方案配备了光纤模块,作为具有现场操作的模块化系统的通用接口。我们以基于硬件的线圈压缩和轨迹提取的并行成像和现场传感为例,说明了该平台的实用性。预处理后的数据分别用于基于扩展编码模型的单镜头和分段螺旋图像重建,分别用于时间序列和解剖成像。

索引关键词:实时处理;光链路;锁相;SoC;FPGA;线圈压缩;k空间轨迹;单镜头成像;磁场监测;螺旋成像;B0校正;扩展编码模型。

- 引言

在当今的磁共振成像(MRI)扫描仪中,具有多达64个线圈的阵列已成为临床标准。为了获得更高的图像质量,提高成像速度[1],[2],[3],[4],[5],目前利用更多元素的阵列成为趋势[6],[7]。但是,这增加了布线的复杂性并且延伸出信号质量和安全性有关的问题[8]。为了解决这个问题,可以在线圈附近进行采集和第一级数据处理。移动光谱仪的内孔[9],[10],[11],模拟成像信号被转换为数字数据流,并以光学方式[9],[10],[11]或使用无线链路传输[12]。

随着射频(RF)通道数量的增加,数据量正在迅速增长,这对吞吐量和数据处理提出了严峻的挑战。通过采用先进的成像协议,如单次扫描读出[13],[14],[15]或零回声时间(ZTE)成像[16],[17],实现了高采集占空比和模拟信号带宽,进一步增加了数据负载。例如,获取32个频道具有1 MHz带宽和每个样本16位I / Q的信号流已经产生了大约128 MB / s的数据流将被传输和连续存储。因此,为了将必须处理的数据量保持在可管理的范围内,数据链[18],[19]中必须对数据进行预处理和压缩。

此外,MRI扫描仪也日益完善带有的传感器,例如用于导管跟踪[20],运动校正[21],[22],[23]和现场监视[24],[25],[26],[27],[28]的有源标记以及基于其他技术的传感器,例如运动跟踪摄像机[29],[30],[31],[32],呼吸和心脏触发系统[33],[34],脑电图[35]和眼动追踪[36]。这些传感器不仅导致了不断增长的数据压力,而且需要系统同时传送需要严格同步的数据和处理各种不同类型的数据。例如,来自眼睛跟踪器[36],运动跟踪器[30]和磁场探头[27],[37],[38]的传感器数据需要同步获取所有数据类型。如果将传感器数据用于扫描仪操作的运行时调整,则必须在严格的延迟约束下执行处理步骤。这些方案包括生理诱导场[39]的稳定化、分段摆振[40]、基于活性标记[21]、[22]、[23]等前瞻性运动校正以及光学方法[29]、[31]、[32]。随着更复杂的梯度矩阵[42]、匀场系统的部署,精确控制和快速反馈的重要性将进一步提高[41]。

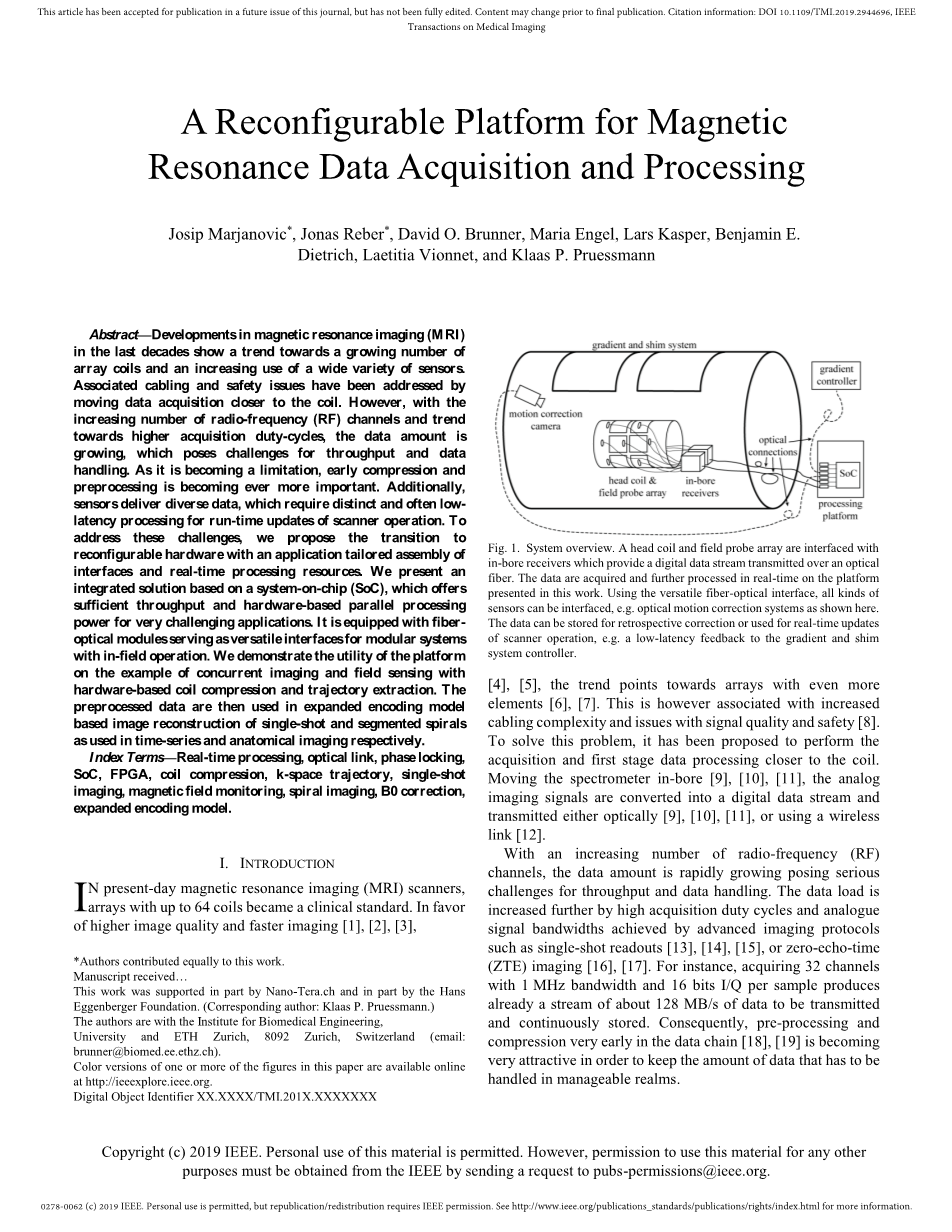

越来越多数据的同步采集和实时处理需要更大的灵活性、吞吐量和更强大的处理能力,这要求研究者必须重新考虑传统的整体式采集系统架构。为了满足所有这些要求,我们建议利用可重新配置的硬件拓扑,以允许应用程序在运行时量身定制接口,实时处理管道和计算资源的组装。我们提出了一个基于单个芯片上系统(SoC)的方法,该片上集成了物理数据接口和可配置的、硬件流水线、高度并行计算能力。最小化内部接口的数量、缓冲和处理开销使系统能够处理非常高的数据吞吐量,并将所涉及的延迟降至最低。该平台配备了通用接口,可以同步采集高吞吐量的数字数据流。以光纤模块的形式,它们解决了可能在现场运行的设备向异构和模块化系统发展的趋势(图1)。

图1 系统总览。头线圈和场探头阵列与孔内接收器接口,孔内接收器提供通过光纤传输的数字数据流。数据将在此工作中介绍的平台上实时获取并进一步处理。使用通用的光纤接口,可以连接各种传感器,例如光学运动校正系统,如图1所示。可以存储数据以进行追溯校正,或用于扫描仪操作的实时更新,例如向梯度和匀场系统控制器的低延迟反馈。

我们以实时线圈压缩和k空间轨迹提取的并发成像和场感测为例,演示了该平台的实用性。数据用于时间序列功能MRI(fMRI)[13],[14],[15]建议的基于扩展编码模型的单发读数图像重建。实时处理表明可以节省大量数据,这是时序成像的一个常见限制。此外,多张图像显示了来自不同来源的分段数据的高度一致性和同步性。

- 方法

A 硬件平台

平台的关键组件(图2)是SoC(Zynq- 7045,Xilinx,美国加利福尼亚州圣何塞),安装在可商用的模块系统(SoM)(Zynq mini module plus,Avnet,Phoenix,AZ)上, 美国)。它在单个芯片上结合了功能强大的处理器(英国剑桥的双核ARM Cortex-A9)和现场可编程门阵列(FPGA)(Kintex,Xilinx,圣何塞,美国加利福尼亚州)。收发器(GTX)连接到六个光纤模块(P1RX6B / P1TX6B,Inneos,美国普莱森顿,美国)。作为非电流连接,它们适合与干扰最小的现场模块进行接口。单根光纤利用波分复用技术将四个高速单向(4 x 3.125 Gbps)和一个双向(1 x 1 Gbps)通道组合在一起。利用可编程高速多路复用器(DS42MB200,德州仪器,达拉斯,德克萨斯州,美国)可灵活利用可用通道,从而在数据接收,吞吐量和其他接口的可用模块数量之间取得平衡。

图2 平台硬件概述。 前面板(a)和后面板(c)以内部视图(b)示出。 该平台的核心组件是SoC,用于同时并实时处理来自不同来源的大量通道。 为了连接光谱仪和现场运行的各种传感器,使用了六个高通量光纤模块。 多模光纤在一个通道上传送一个低抖动时钟,以使外部模块与平台同步。 时钟是使用带有外部VCXO的双PLL芯片产生的。 参考时钟由高质量的OCXO,GPS天线或外部提供。 TTL容限触发界面用于将平台操作与扫描仪同步。 该平台具有许多其他有用的接口,例如用于数据存储的SATA,用于远程访问和数据传输的以太网,高吞吐量并行接口,USB,SD卡插槽和显示端口。

在SoC中处理的数据要么用于更新扫描仪操作,要么存储用于图像重建和评估扫描仪硬件。为此,有几个选项可用。两个光纤发送器模块提供了低延迟连接,适合现场稳定中使用的实时反馈[39]。千兆以太网允许通过标准个人计算机(PC)图形用户界面(GUI)控制的平台独立运行。SATA接口可将数据直接存储在固态驱动器上。或者,并行接口允许将完整的原始数据带宽流传输到另一个数据聚合设备。为了同步连接的现场模块,每个光模块在一个通道上提供一个低抖动时钟信号。它是利用超低相位噪声时钟发生器生成的,该时钟发生器基于双相锁相环(PLL)(LMK04828,德州仪器(TI),达拉斯,德克萨斯州,美国)和外部压控晶体振荡器(VCXO)(CVHD-950,美国佛罗里达州迈尔斯堡的Crystek)。参考时钟来自10 MHz参考时钟输入(通常用于将平台与扫描仪时钟同步),带有GPS天线的全球定位系统(GPS)约束振荡器(GPSDO)模块或烤箱控制的源。晶体振荡器(OCXO)(AOCJY6,Abracon,美国德克萨斯州Spicewood)。OCXO的自主选件提供了高质量时钟,在10 Hz至1 MHz范围内集成了185 fs的抖动。它可用于通过平台的参考时钟输出同步外部设备。

B 芯片系统

SoC由两部分组成-可编程系统和可编程逻辑(FPGA)(图3)。可编程系统是功能齐全的微控制器系统,可以独立运行它由具有常用内核(例如定时器,中断控制器,SPI,IIC,SDHC,UART,以太网,USB和SDRAM存储器控制器)的处理器组成。它们通过系统总线(AXI4-MM,ARM,英国剑桥)与处理器连接。它用于访问内核的寄存器,这些寄存器映射为存储器空间。内核的功能可以通过一组读写来控制,这些读写以软件功能和抽象驱动程序的形式组织。

可编程系统和逻辑与多个系统总线(AXI4-MM)连接,使可编程逻辑成为可编程系统内核的自然扩展,可以灵活地进行设计。通过将部分功能移至软件,该方法可实现对FPGA设计的高级软件控制,并具有更大的灵活性。此外,它还可以重用内核,使用第三方内核以及轻松且合规的集成,从而缩短了总体开发时间。

该系统通过定制的FPGA内核支持平台的高速光接口,相关数据流的处理以及大规模实时数据处理,通信和排序。所有内核均已用VHDL编写,并已在MATLAB中使用位真正的模型进行了验证。表I中给出了造成的资源利用,下面是对设计内核的更详细描述。

图3 SoC由可编程系统和逻辑部分组成。可编程系统是一个双核处理器(ARM A9),具有常用的内核,如SPI,IIC,USB,以太网,SDHC,计时器,中断控制器,以太网和SDRAM的存储控制器。处理器通过系统总线(AXI4-MM)与内核进行通信,该系统总线也用于访问可编程逻辑(FPGA)。 因此,它是可编程系统内核的定制设计扩展。在该项目中,它用于同时并实时地对大量数据流和通道进行数据流路由(蓝色)和信号处理(绿色)。

- 高速数据连接

为了连接平台的光模块,已经定制了高速数据链路核心。它基于Aurora内核(Xilinx,美国加利福尼亚州圣何塞),带有附加的寄存器接口,用于错误监视,软件重置和链接初始化。该内核的主要目的是利用嵌入式GTX收发器进行数据序列化和反序列化,该收发器以3.125 GHz的行业标准运行。数据通过流式32位宽并行接口在内核之间传输。它们以156.25 MHz的时钟频率工作,这对应于使用标准8b10b直流(DC)平衡的两个通道中每个通道的二十倍数据串行化。整个设计中使用的频率与数据处理时钟相同。该接口以简单的点对点协议(AXI4-Stream,ARM,英国剑桥)的形式实现。它具有嵌入式数据流控制功能,该功能在所有信号处理内核中均可使用,以在数据流损坏时引发错误标志并中断处理器。

- 存储接口

内部数据交换主要使用高效的流接口来实现,以防止不同操作之间的瓶颈。但是,在某些情况下,需要处理器和可编程逻辑之间的大缓冲区和共享内存。这尤其是为了将FPGA的并行处理能力与处理器在软件中执行复杂操作的能力结合在一起。

因此,已经开发出一种存储器访问核心,以将数据从流式体系结构传输到存储器,并以另一种方式使用51.2 Gbps的带宽传输到SDRAM存储器。从而提供了四个主从流接口(AXI4-Stream)和一个到存储器映射总线的主接口(AXI4-MM主站)。后者连接到可编程系统部件(AXI4-MM),后者可以访问与SDRAM接口的存储器控制器。存储器位置,数据选择和块大小可以通过寄存器设置来定义,并且在完成块传输以进行流控制时可以引发中断。

- 流量交换

为了实现信号处理操作的级联和数据流的灵活路由,已经开发了流互连核心。它最多可连接32个从属和主流(AXI4-Stream)接口,它是所有数据通过的中心点。因此,这是至关重要的部分,它对整个FPGA设计的布局和布线具有很大的影响。它利用了多个流水线阶段和先进的多路复用器架构,以简化数字设计的时序收敛。

- 流量融合

为了联合处理和存储公共源数据,已经开发了流融合核心。它将多达四个数据流融合为一个数据流,包括先前的通道选择。这涵盖了所有四个光学模块连接到同一数据源的情况,例如四个孔接收器[10]连接到64通道线圈。

- 并行接口

并行接口核心提供高吞吐量,足以以全带宽将数据从所有光学模块传输到主机。由于GTX资源稀缺,而是用于连接平台的光模块,因此使用了通用引脚。它们可以在高达1 GHz的频率下运行,用于最小化通道数。四个流接口(AXI4-Stream)的数据和控制信号经过5b6b编码以进行DC平衡,并串行化为工作在937.5 MHz的并行数据流。它通过放置在平台背面的两个电缆连接器进行传输。

- 相位幅度提取

基于核磁共振(NMR)作为NMR活性标记的场传感器[20],[21],[22]和场监视探头[24],[25],[26],[27],[28],[ [23]依赖于在脉冲NMR实验中产生的自由感应衰减(FID)信号的测量。FID的相位与传感器位置处的磁场的时间积分成正比,这是k空间编码的理想值。因此,现场感测的第一步是评估已经开发了专用内核的信号相位。

它基于圆形矢量模式下的坐标旋转数字计算机(CORDIC)。它使用简单的移位和加法运算来执行基本旋转,从而依次逼近复杂信号的相位和幅度[43],[44],[45]。为了获得最大的数值精度和完整的吞吐量,它以流水线方式执行32次迭代。幅度和相位结果分为两个单独的数据流(AXI4-Stream),因为对于这两种数据类型,进一步的处理通常有所不同。

内核具有许多可选的附加功能,如下所示。为了直接获得磁场值而不是时间积分,可以对相位进行微分,可以将其展开以进行进一步处理,并且可以通过对非展开相位

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[236474],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。