英语原文共 9 页,剩余内容已隐藏,支付完成后下载完整资料

- 硬件

—硬件

概述

8051 系列微处理器基于简化的嵌入式控制系统结构,被广泛应用于从军事到自动控制再到 PC 机上的键盘上的各种应用系统上。仅次于 Motorola 68HC11 在 8 位微控制器市场上的销量,很多制造商都可提供8051系列单片机,像Intel,Philips,Siemens等。这些制造商给 51 系列单片机加入了大量的性能和外部功能,像总线接口,模拟量到数字量的转换,看门狗,PWM输出等,不少芯片的工作频率达到40M,工作电压下降到1.5V。基于一个内核的这些功能使得 8051 单片机很适合作为厂家产品的基本构架,它能够运行各种程序,而且开发者只需要学习这一个平台。

- 系列的基本结构如下:

- 一个8位算术逻辑单元

- 32个I/O口 4组8位端口 可单独寻址

- 4两个 16 位定时计数器

- 全双工串行通信

- 6 个中断源 两个中断优先级

- 128字节内置 RAM

- 独立的64K字节可寻址数据和代码区

每个8051处理周期包括12个振荡周期,每12振荡周期用来完成一项操作,如取指令和。计算指令执行时间可把时钟频率除以12,取倒数,然后指令执行所须的周期数,因此,如果你的系统时钟是11.059MHz,除以12后就得到了每秒执行的指令个数,为921583条指令,取倒数将得到每条指令所须的时间1.085ms。

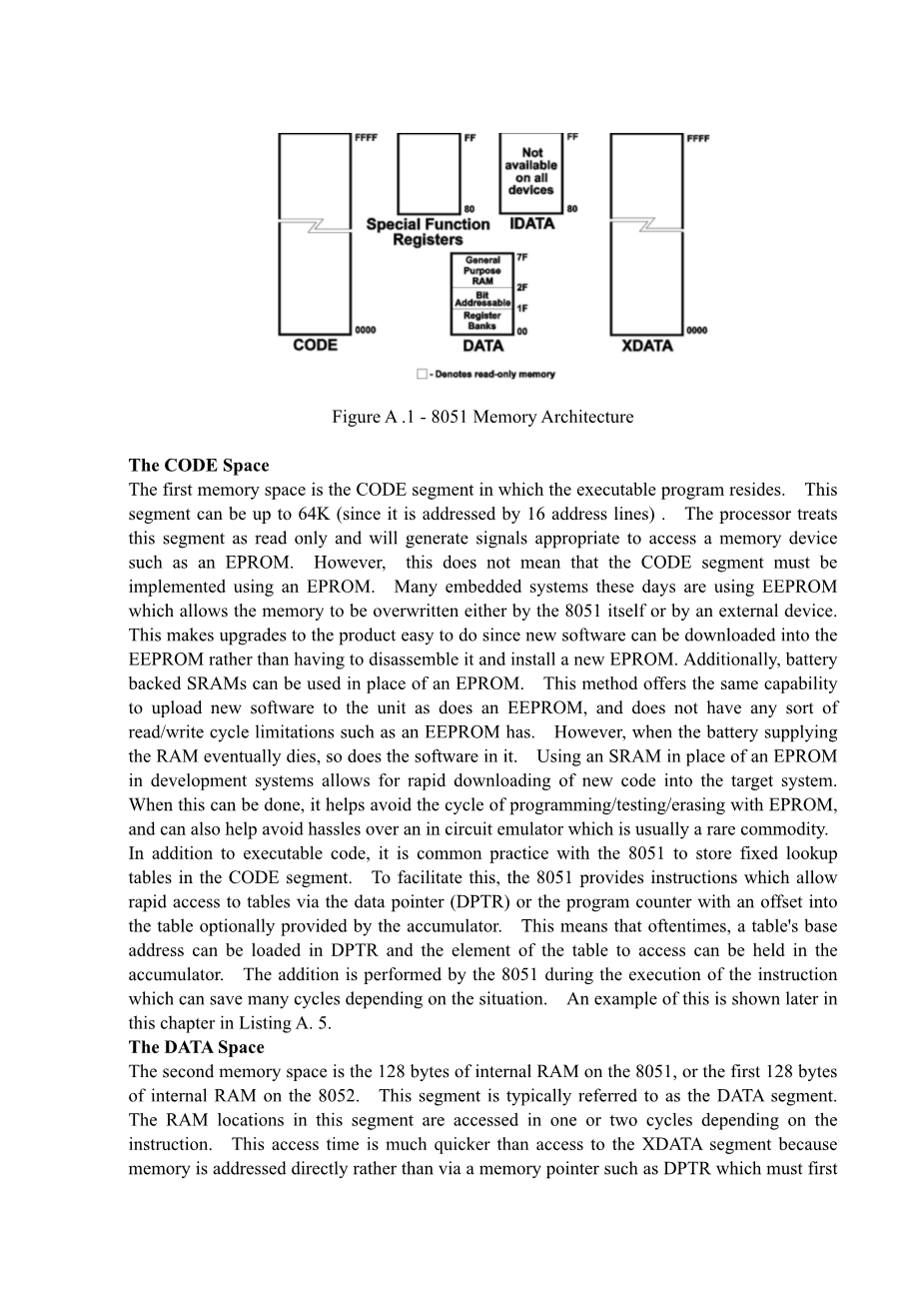

图 A1-8051 存储结构

CODE区

第一个存储空间是代码段,用来存放可执行代码。被16位寻址,空间可达64K。代码段是只读的,当要对外接存储器件如EPROM进行寻址, 处理器会产生一个信号。但这并不意味着代码区一定要用一个EPROM。目前,一般使用EEPROM作为外接存储器,可以被外围器件或 8051进行改写。这使系统更新更加容易,新的软件可以下载到EEPROM中,而不用拆开它,然后装入一个新的EEPROM。另外,带电池的SRAMs也可用来代替EPROM,他可以像 EEPROM一样进行程序的更新,并且没有像EEPROM那样读写周期的限制。但是,当电源耗尽时,存储在SRAMs中的程序也随之丢失。使用SRAMs来代替EPROM时,允许快速下载新程序到目标系统中,这避免了编程/调试/擦写这样一个循环过程,不再需要使用昂贵的在线仿真器。

除了可执行代码,还可在代码段中存储查寻表,为达此目的,8051提供了通过数据指针 DPTR 或程序计数器加上由累加器提供的偏移量进行寻址的指令,这样就可以把表头地址装入 DPTR中,把表中要寻址的元素的偏移量装入累加器中,8051在执行指令时的过程中把这两者相加,由此可节省不少指令周期。

DATA区

第二个存储区是8051内128字节的内部RAM,或8052的前128字节内部RAM。这部分主要是作为数据段,称为 DATA区。指令用一个或两个周期来访问数据段。访问DATA区比访问XDATA区要快,因为它采用直接寻址方式,而访问XDATA须采用间接寻址,必须先初始化 DPTR。通常我们把使用比较频繁的变量或局部变量存储在DATA段中,但是必须节省使用DATA段,因为它的空间毕竟有限。

在数据段中也可通过R0和R1采用间接寻址,R0和R1被作为数据区的指针,将要恢复或改变字节的地址放入R0或R1中,根据源操作数和目的操作数的不同,执行指令需要一个或两个周期。

数据段中有两个小段,第一个子段包含四组寄存器组,每组寄存器组包含八个寄存器,共32个寄存器,可在任何时候通过修改PSW寄存器的RS1和RS0这两位来选择四组寄存器的任意一组作为工作寄存器组,8051也可默认任意一组作为工作寄存器组。工作寄存器组的快速切换不仅使参数传递更为方便,而且可在8051中进行快速任务转换。

另外一个子段叫做位寻址段BDATA,包括16个字节,共128位,每一位都可单独寻址。8051有好几条位操作指令,这使得程序控制非常方便,并且可帮助软件代替外部组合逻辑,这样就减少了系统中的模块数。位寻址段的这16个字节也可像数据段中其它字节一样进行字节寻址。

特殊功能寄存器

中断系统和外部功能控制做特殊功能寄存器,简称SFR。其中很多寄存器都可位寻址,可通过名字进行引用。如果要对中断使能寄存器中的EA位进行寻址,可使用EA或IE.7或0AFH。 SFRs控制定时/计数器,串行口,中断源及中断优先级等。这些寄存器的寻址方式和DATA取中的其它字节和位一样。可位寻址 SFR如表 A-1所示。

表 A.1 可进行位寻址的 SFR

IDATA区

8051系列的一些单片机如8052有附加的128字节的内部RAM,位于从80H开始的地址空间中,被称为IDATA。因为 IDATA区的地址和SFRs的地址是重叠的,通过区分所访问的存储区来解决地址重叠问题,因为IDATA区只能通过间接寻址来访问。

XDATA区

8051的最后一个存储空间为64K,和CODE区一样,采用16位地址寻址,称作外部数据区,简称XDATA区。这个区通常包括一些RAM(如SRAM)或一些需要通过总线接口的外围器件。 对XDATA的读写操作需要至少两个处理周期,使用DPTR,R0或DPTR,R1。对DPTR来说,至少需要两个处理周期来装入地址,而读写又需要两个处理周期。同样,对于R0或R1装入需要一个以上的处理周期,而读写又需两个周期,由此可见,处理XDATA中的数据至少要花3个指令周期,因此,使用频繁的数据应尽量保存在DATA区中。

如果不需要和外部器件进行I/O操作或者希望在和外部器件进行I/O操作时开关RAM,则XDATA可全部使用64K RAM。

位操作和布尔逻辑

8051可分别对BDATA和SFRs中128个可寻址位,32个 I/O口进行位逻辑操作。可对这些位进行与,或,异或,求补,置位,清零等操作,并可像转移字节那样转移位。

可寻址位也可作为条件转移的条件,一条很有用的指令就是JBC,通过判断可寻址位是否置位来决定是否进行转移,如果该位置位则转移,并清零该位。这条指令能够在两个处理周期中完成,比在两个代码段中分别使用跳转和清零指令要节省一到两个处理周期。比如说,你要编写一个过程,等待P0.0置位,然后跳转,但是等待有时间限制。这样就需要设置一个时间,时间到达后跳出查询,检测到 P0.0 置位后跳出,并清零 P0.0。

寻址方式

8051 可对存储区直接或间接寻址。这些是典型的寻址方式。直接寻址是在指令中直接包含所须寻址的字节地址,直接寻址只能在DATA区和SFR中进行。 间接寻址要使用DPTR,PC, R0, R1寄存器,用来存放所要访问数据的地址,指令使用指针寄存器,而不是直接使用地址。用间接寻址方式可访问CODE IDATA XDATA存储区。对DATA存储区也可进行间接寻址。只能用直接寻址方式对位地址进行寻址。

在进行块移动时,用间接寻址十分方便,能用最少的代码完成操作。可以利用循环过程使指针递增。对CODE区进行寻址时,将基址存入DPTR或 PC中,把变址存入累加器中,这种方法在查表时十分有用。

处理器状态

处理器状态保存在一个称为位寻址SFR PSW(处理机状态字)。这个寄存器包含进位,用BCD码操作的辅助进位,蓄能器奇偶标志位,溢出标志位, 两个一般标志位和两个默认注册位。如前所述,该寄存器组选择位由0至3的数字组成,这说明该页面要可以使用。页面0从数据段中的底部开始(地址00H),页面1从地址08H开始,页面2从地址10H开始,页面3从地址18H开始。 无论寄存器页面如何选择,这些内存的任意位置都可以通过他们的地址访问。PSW的布局如下:

处理器状态字(PSW)-位寻址

表A.2

|

CY |

AC |

F0 |

RS1 |

RS0 |

0V |

USR |

P |

CY 进位标志

AC 辅助进位标志

F0 通用标志位

RS1 寄存器页面选择1、MSB选择器

RS0 寄存器选择页面2、LSB选择器.

OV 溢出标志

USR 用户定义的标志

P 奇偶标志

电源控制

8051的CHMOS版本可通过软件设置两种节电方式,空闲模式和低功耗模式。设置电源控制寄存器PCON的相应位来进入节电方式。置位IDLE进入空闲模式,空闲模式将停止程序执行, RAM中的数据仍然保持,晶振继续工作,但与 CPU 断开。定时器和串行口继续工作。发生中断将退出中断模式。执行完中断程序后,将从程序停止的地方继续指令的执行。

通过置位PDWN位来进入低功耗模式,低功耗模式中晶振将停止工作,因此,定时器和串行口都将停止工作。至少有两伏的电压加在芯片上,因此,RAM中的数据仍将保存。退出低功耗模式只有两种方式,上电或复位。

SMOD位可控制串行通信的波特率,将使由定时器1的溢出率或晶振频率产生的波特率翻倍。置位SMOD可使工作于方式1,2,3定时器产生的波特率翻倍。当使用定时器2产生波特率时,SMOD将不影响波特率。

功率控制寄存器(PCON)-不可位寻址

表A.3

|

SMOD |

- |

- |

- |

GF1 |

GF0 |

PDWN |

IDLE |

SMOD 串口波特率发生器模式,如果SMOD = 1,UART的波特率翻倍

- 保留

- 保留

- 保留

GF1 通用标志位

GF0 通用标志位

PDWN 掉电标志位,设置这一位使功率下降模式激活

IDLE 空闲标志位,设置此位使空闲模式激活

中断系统

基本的8051支持6个中断源,两个外部中断,两个定时/计数器中断,一个串行口输入/输出中断。中断发生后,处理器转到将五个中断入口处之一执行中断处理程序。中断向量位于代码段的最低地址出(串行口输入,输出中断共用一个中断向量)。中断服务程序必须在中断入口处或通过跳转,分支转移到别处。8051/8052的中断向量表 A.4:

|

中断源 |

中断向量 |

|

上电复位 |

0000H |

|

外部中断 0 |

0003H |

|

定时器 0 溢出 |

000BH |

|

外部中断 1 |

0013H |

|

定时器 1 溢出 |

001BH |

|

串行口中断 |

0023H |

|

定时器 2 溢出 |

002BH |

8051支持两个中断优先级,有标准的中断机制,低优先级的中断只能被高优先级的中断所中断,而高优先级的中断不能被中断。

中断优先级寄存器

每个中断源都可通过设置中断优先级寄存器IP来单独设置中断优先级。如果每个中断源的相应位被置位,则该中断源的优先级为高如果相应的位被复位,则该中断源的优先级为低。表5显示了IP寄存器及其位分配。请注意,该寄存器有位可寻址。

中断优先级寄存器(激)位可寻址

表A.5

|

- |

- |

PT2 |

PS |

PT1 |

PX1 |

PT0 |

PX0 |

- 保留

- 保留

PT2 定时器2溢

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[147295],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。