英语原文共 4 页,剩余内容已隐藏,支付完成后下载完整资料

基于IRIG-B时间码的解码装置设计

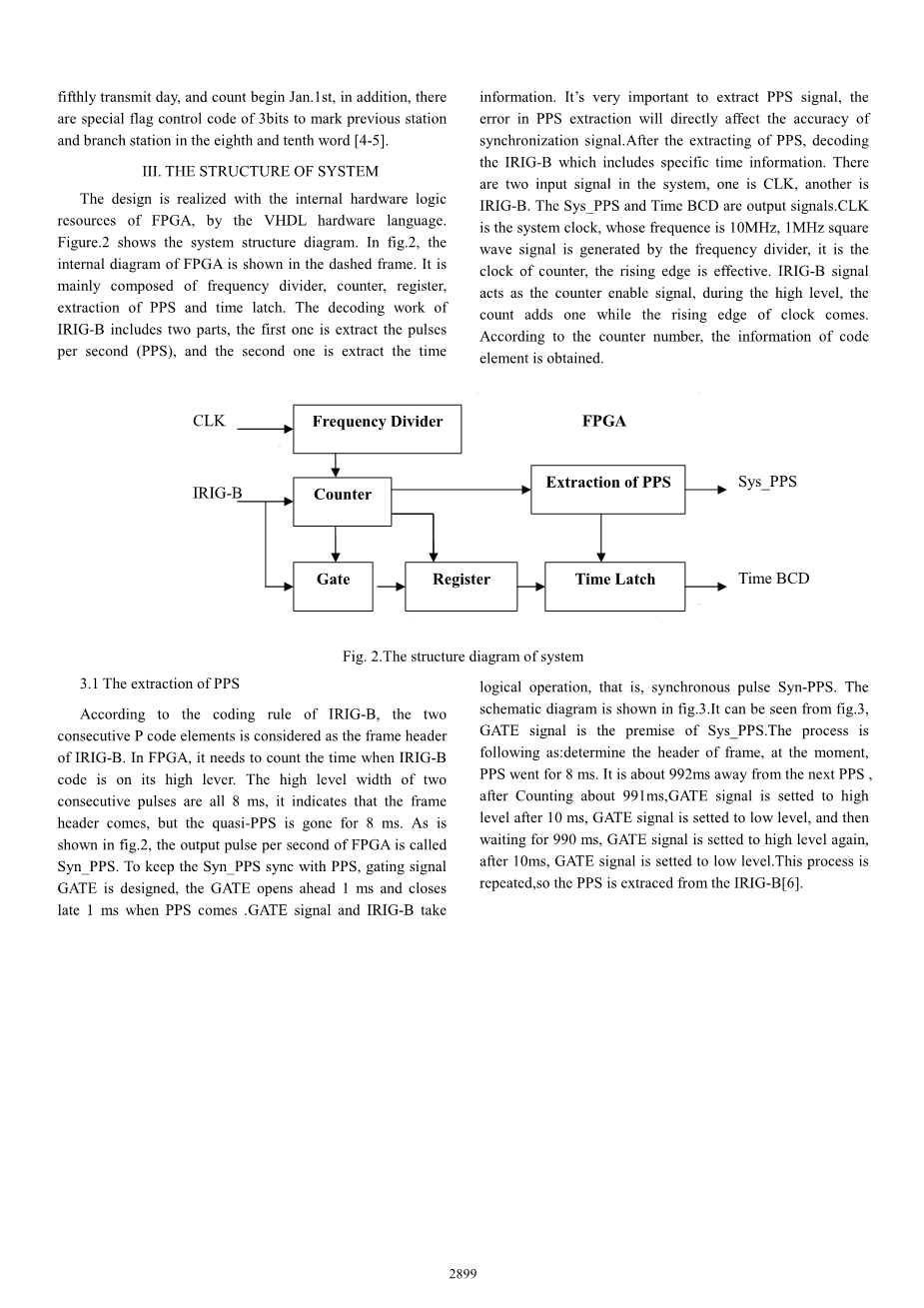

周国平 屈少军 许严

- 南京林业大学,南京,中国

- 中信网络通信教育中心,深圳,中国

E-mail: zhougp@njfu.com.cn

概述:IRIG-B时间码作为国际通用的时间编码序列,广泛使用在各类时间同步系统中。译码电路提出了利用单片机为核心结合具有数字模拟转换电路的外围控制电路来解码IRIG-B时间码。该电路将解码出年、月、日,小时,分钟,秒等时间信息并发送到外围设备并通过串行端口输出,以实现各设备之间的时间同步并输出标准的秒脉冲信息。

关键词:IRIG-B码;时间同步;秒脉冲;解码

1.背景介绍

鉴于电力系统和自动化水平不断提高,国家电网公司加强了对电力二次系统时钟管理的重视程度并对时间同步系统与系统时钟装置精度提出了更高的要求。目前,大部分时间信息传递使用IRIG-B码,但时间设定装置需要B码解调时间信息。在电力系统自动化领域,GPS的应用时间同步设置技术提供了准确的系统时间,该技术符合中国的电力系统的发展需求,同时对提高电能质量、优化电网调度、准确分析事故、加强电网运行的同步监测与运行条件的控制具有十分重要的意义。

2.IRIG-B码的格式规范

IRIG(靶场仪器组)是U.S. RCC(靶场指挥委员会)的附属单位,它指定的时间编码格式分为两类,一类是并行时间代码格式,另一种是串行时间代码格式。IRIG串行时间码格式共有七类,分别是IRIG-A, B, C,D,E,G 和H码。其中,IRIG-C已被IRIG-H所取代。现有的六种时间码主要区别在于它们帧速率的不同。在时间帧周期的基础上,大于1秒有D,E,F三种格式的时间码。由于速度较慢,这些代码主要用于磁带记录等。高码元速率的IRIG-A和G两种格式的时间码,可以直接用于获取较高的时间分辨率。IRIG-B格式时间码的速率为每秒一帧。发送的时间信息不仅包含秒脉冲信息,还包括最适合人们使用的绝对时间比如年、日、分、秒等二进制信息。因此,在对六种IRIG串行时间码格式中,B码的使用最为广泛。B码基本的码元信号频率为100HZ,位置识别标志出现频率为10HZ。B码速率为每秒一帧。不同的码元分别由不脉宽的脉冲信号表示,脉宽为2毫秒的脉冲代表二进制数字lsquo;0rsquo;,脉宽为5毫秒的脉冲代表二进制数字lsquo;1rsquo;,而脉宽为8毫秒的脉冲则代表位置识别标志P。三类码元示意图如图1所示。

10毫秒

10毫秒

10毫秒

8毫秒

5毫秒

2毫秒

图1.IRIG-B码元示意图

天时间二进制码

特殊控制码元

年

日

时

分

秒

位置标识符

索引间隔

标准时间起点

参考位置标记

二进制0

索引标记

二进制1

起始参考位

图2.线性IRIG-B码示意图

图2显示了IRIG-B码示意图(DC码)。它是一个每秒一次的串行时间码,每个码元脉宽为10毫秒,在一帧周期内有100个码元,叫做脉冲宽度编码,每个码元都有三种模式:二进制0、1和位置标识符。它分为3个字段编码:第一字段为年份(年,日,小时,分钟和秒);第二个字段是控制函数域;第三段是表示天时间的二进制码。他们每24小时循环一次。每个码元脉冲的上升沿表示该码元所包含时间信息的准点信息。两个连续的脉冲宽度为8毫秒的位置标识符中第二个位置标识符的上升沿即当前时间的准点时刻。每十个码元中最后一位都是位置标识符,故1秒内共有十个位置标识符。即:P1,P2,P3,hellip;,P9、P0。他们都是是8毫秒脉冲宽度;PR是每帧数据的起始位参考点,二进制“1”和“0” 分别对应5毫秒和2毫秒脉冲宽度。上一帧数据的码元中最后一个脉宽8毫秒的码元与下一帧帧头8毫秒的码元相连,代表新一帧的数据传输开始。

3. IRIG-B时间码解码设计方案和硬件电路设计

IRIG-B格式时间码解码方法为从IRIG-B码中提取秒,小时,日,月,年等并转化成二进制时间信息,然后再将二进制信息转换成其他时间设置设备可识别的时间格式。以帧起始位参考点的上升沿为参考,装置产生的秒脉冲信息并同时串行输出信息。解码的关键在于检测每个码元的高电平宽度。

A设计方案

大多数计时设备产生的IRIG-B(DC)码为RS422/RS485接口信号。所以,通过检测高电平宽度,我们首先将IRIG-B时间码信息转换成TTL电平输入到89C52单片机片机INT0端口。然后我们必须检测两次连续的8毫秒脉宽的码元所在的位置来确定新一帧的开始并开始计数码元,然后检测随后的98个码元的脉冲宽度。当INT0端口由低电平变为高电平时,应启动单片机内部定时器T0并打开T0中断,将T0定时为0.5毫秒。每次T0中断,计数器加1。当INT0端口变化由高电平变为低电平,就关闭T0中断,读取计数器的数值。脉冲宽度等于计数值乘以0.5毫秒;最后,根据高电平宽度来解码对应的IRIG-B码元信息。进而形成秒、分、时、日和年的BCD码和表示天时间的二进制码。所有这些信息存储在单片机内部RAM单元,输出1pps、1ppm、1pph信号和232BJT电平。整体设计解码装置图如图3所示。

(232)

BJT

TTL/232

IRIG-B

1PPS/1PPM/1PPH

I/O和显示模块

微机解码 模 块

232串口模块

图3.解码装置整体设计框图

B.硬件电路设计

图4.解码电路原理图

IV.软件设计

在程序设计中,考虑到解码出的时间信息已经落后于解码设备从时间终端接收到的并本应解码出的当前时间信息,因此,必须添加额外的1秒到当前解调时间,然而,添加一秒钟的时间信息将导致日,月,年等时间信息的变化。此外大月、小月、闰月、平年和闰年等其它时间信息的影响将使解码时间信息变得更为复杂。所以所有这些可能导致时间信息变化的因素都需要在编程过程中充分考虑。我们编制了相应的处理子程序例如有的子程序用来判断闰年,有的子程序用于在天数和日期之间转换等等。后经反复验证,解码装置输出的时间信息准确可靠,时间精度为1微秒。

- 主程序

这个程序输通过串口中断程序出解码的时间信息,同时从P1.5脚输出脉宽为100毫秒秒脉冲的的信息。主程序如图5所示。时间校对子程序与主程序相似。它通过不发送秒脉冲信息和启动串口中断来进行延时。时间校对子程序是在获得准确完整的时间信息后再输出,以保证时间信息的准确性。串口中断程序循环发送处理后的时间信息,并存放在连续的存储单元中。

8ms计数器加1

P3.2=1?

启动T0

P3.2=1?

调用时间处理子函数

调用首次同步子函数

程序初始化

是

8ms计数器值为1?

T0设置初值为0.5毫秒,串口输出数据,装载起始地址

否

否

8ms计数器值为2?

是

T0初值设为0.5ms

是

置入帧头标记

重置8ms计数器

P3.2=1?

是

否

增加码元数

否

启动T0

否

码元数=10?

是

P3.2=0?

是

是

否

P3.2=0?

否

P1.5中断输入

从P1.5输出秒脉冲,开启中断程序

码元数=98?

否

是

是

P3.2=1?

是

重置帧头标志和码元数

否

否

R7寄存器装载计数值并重置计数器

关闭T0计数器,停止计数

是

调用以脉宽为判断依据的装载记忆子函数

帧标记=1?

是

否

R7gt;13?

否

重置8ms计数器

图5. IRIG-B码解调框图程序

- 子程序

- 子程序从IRIG-B码和单片机的RAM定义列表中提取年月日等时间信息。将IRIG-B码发送到单片机INT0侧。在单片机的初始化设置期间,定时器T0作为模式1的内部时钟。当INT0引脚电平从低到高,定时器T0开始计时。在0.5毫秒结束后,芯片开启T0中断,T0中断程序以每0.5毫秒加一的方式计数,当INT0引脚电平从高电平到低电平时的T0停止计数,通过读取计数值来计算INT0引脚高电平宽度,最终以BCD码形式生成秒,分钟,小时,天,年等时间信息。

表I.单片机内存定义表

|

帧标记 |

00H |

|

闰年标记 |

02H |

|

秒、分时位置单元 |

21H、22H、23H |

|

天个位、十位、百位位置单元 |

24H、25H |

|

年、年10位位置单元 |

26H |

|

二进制天时间计数 |

27H、28H、29H |

|

8ms计数器 |

30H |

|

0.5ms计数器 |

31H |

|

同步时间计数器 |

32H |

|

码元 |

33H |

|

BCD码转二进制寄存器 |

34H、35H |

|

时-分-秒ASCII码 |

41H-3CH |

|

天个位、十位、百位ASCII码 |

45H-42H |

|

年-月-日ASCII码 |

46H-4BH |

- 图6所示子程序展示了秒位加法的处理。

是

是

是

否

否

否

是

否

是

否

是

否

是

是

否

否

出栈并返回

图6.秒数增加子程序

在大多数情况下,时间信息滞后于收到的时刻。所以为了保证时间信息的准确性,在下一个秒脉冲到来前,接收到的秒数加一,以便在下一秒脉冲到来时输出修正过的时间信息。此外,时间信息后添加1秒可能会导致

分钟、小时、日、月、年的波动。一个简单的例子就是跨年时刻也与闰年和非闰年的差别或者二月推迟与三月提早有关。

- 子程序说明如何将年月日信息转化成一年天数信息。

IRIG-B码包含一年内的天数的时间信息,而北京时间的格式不包括这些。因此加一秒处理后的月、日信息和闰年的判断应基于格林尼治标准时间格式语句下的月和日期信息,然后将上述信息转化成一年中的某一天。

V.总结

近年来,一些电力系统为基础的行业对时间的精准度提出了高地要求。许多企业引进国外先进的校对时间终端来满足他们的时间精确性的要求。而西欧,美国和其他发达地区国家采用IRIG-B编码输出格式产生时间校对终端。为了适应中国的时间格式和扩大IRIG-B码的应用范围,本文提出了一种以单片机处理器为核心,结合外围控制电路和D/A转换电路的IRIG-B码解码装置。与其他同类产品相比,本设计具有较高的应用价值,解码装置性能更加稳定,抗干扰能力强,且体积较小。

参考文献

[1]刘浩素,李丁敏. IRIG时间同步在测控保护装置中的实现[J]. 江苏电气工程, 2007(26) :48-50.

[2]雷振,魏峰. 时间码在GPS同步时钟中的应用[J]. 现代电子技术,2004(5): 75-79.

[ 3 ]朱祖洋,薛冰. 基于IRIG-A的编码输出的微型GPS时钟设计[J]. 单片机与嵌入

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[139470],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。