英语原文共 28 页,剩余内容已隐藏,支付完成后下载完整资料

特性

bull; 单电压读写操作 bull; 自动地址递增(Auto Address Increment, AAI)

– 2.7-3.6V 编程

– 减少字节编程操作期间的总芯片编程时间

bull; 串行接口架构 bull; 写操作结束检测

– 兼容SPI:模式0 和模式3 – 软件轮询状态寄存器中的BUSY

– AAI 模式下SO 引脚上的忙状态读出

bull; 高速时钟频率 bull; 保持引脚(HOLD#)

– 高达50 MHz – 在不取消选择器件的情况下暂停存储器的串行序列

bull; 超高可靠性 bull; 写保护(WP#)

– 可擦写次数:100,000 次(典型值) – 允许/ 禁止状态寄存器的锁定功能

– 数据保存时间大于100 年

bull; 低功耗: bull; 软件写保护

– 读操作工作电流:10 mA (典型值) – 通过状态寄存器中的块保护位实现写保护

– 待机电流:5 mu;A (典型值)

bull; 灵活的擦除功能 bull; 温度范围

– 均一4 KB 扇区 – 商业级:0°C 至 70°C

– 均一32 KB 覆盖块 – 工业级:-40°C 至 85°C

– 均一64 KB 覆盖块

bull; 快速擦除和字节编程: bull; 可用封装

– 全片擦除时间:35 ms (典型值) – 8 引脚SOIC (200 mil)

– 扇区/ 块擦除时间:18 ms (典型值) – 8 触点WSON (6 mm x 5 mm)

– 字节编程时间:7 mu;s (典型值)

bull; 所有所有非铅(无铅)器件均符合RoHS 标准

产品描述

SST 的25 系列串行闪存采用四线、兼容SPI 的接口,从而实现占用较少电路板

空间的低引脚数封装,并最终降低总系统成本。SST25VF016B 器件是增强型器

件,与原有的SST25VFxxxA 器件相比,提高了工作频率并降低了功耗。

SST25VF016B SPI 串行闪存采用SST 专有的高性能CMOS SuperFlashreg;技术

制造。与其他方法相比,分离栅极单元设计(split-gate cell design)和厚氧化层

隧穿注入器(thickoxidetunneling injector)可实现更高的可靠性和可制造性。

SST25VF016B 器件可以显著提高性能和可靠性,同时降低功耗。但对于

SST25VF016B,器件使用2.7-3.6V单电源进行写操作(编程或擦除)。消耗的总

能量是应用中施加电压、电流和时间的函数。对于任何给定的电压范围

SuperFlashreg; 技术的编程电流更低、擦除时间更短;因此,在任何擦除或编程操

作期间消耗的总能量低于其他闪存技术。SST25VF016B 器件提供8 引脚SOIC

(200 mil)和8 触点WSON (6 mm x 5 mm)封装。有关引脚分配,请参见图2。

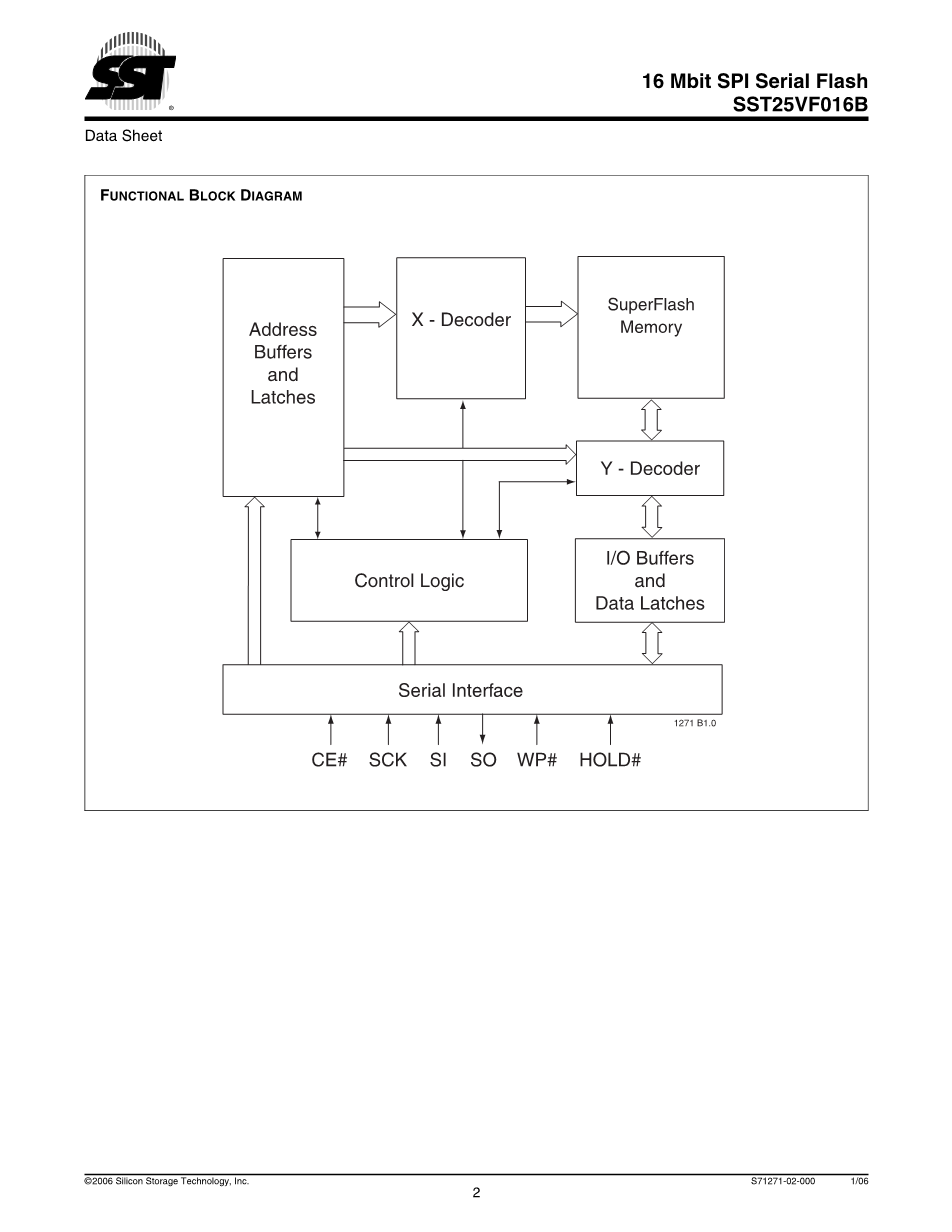

图1: 功能框图

存储器构成

SST25VF016B SuperFlash 存储器阵列由均一4 KB 可擦除扇区以及32 KB

覆盖块和64 KB 覆盖可擦除块组成。

器件操作

SST25VF016B 通过兼容SPI (串行外设接口)总线的协议进行访问。SPI 总

线包含四条控制线;芯片使能(CE#)用于选择器件,数据通过串行数据输入

(SI)、串行数据输出(SO)和串行时钟(SCK)进行访问。

SST25VF016B 支持SPI 总线操作的模式0(0,0)和模式3(1,1)。如图3 所

示,两种模式之间的差异在于当总线主器件处于待机模式并且没有数据传送时

的SCK信号状态。SCK信号在模式0 时为低电平,在模式3 时为高电平。对

于这两种模式,串行数据输入(SI)在SCK 时钟信号的上升沿被采样,串行

数据输出(SO)在SCK 时钟信号的下降沿之后被驱动。

保持操作

HOLD# 引脚用于暂停正在操作SPI 闪存存储器的串行序列,但不会复位时钟序

列。要激活HOLD# 模式, CE# 必须处于有效低电平状态。当SCK 有效低电平

状态与HOLD# 信号的下降沿同时发生时,HOLD# 模式开始。当HOLD# 信号的

上升沿与SCK 有效低电平状态同时发生时,保持模式结束。

如果HOLD# 信号的下降沿未与SCK 有效低电平状态同时发生,则当SCK 再次

达到有效低电平状态时器件进入保持模式。同样,如果HOLD# 信号的上升沿未

与SCK 有效低电平状态同时发生,则当SCK再次达到有效低电平状态时器件退

出保持模式。有关保持条件波形,请参见图4。

器件进入保持模式之后, SO 将处于高阻抗状态,而SI 和SCK 可以为VIL 或VIH。

如果在保持条件期间将CE# 驱动为有效高电平,则将复位器件的内部逻辑。只要

HOLD# 信号为低电平,存储器就会保持在保持条件下。要继续与器件进行通信,

必须将HOLD# 驱动为有效高电平,并将CE# 驱动为有效低电平。有关保持时序,

请参见图24。

写保护

SST25VF016B 提供了软件写保护。写保护引脚(WP#)用于使能或禁止状态寄存

器的锁定功能。状态寄存器中的块保护位(BP3、BP2、BP1、BP0 和BPL)提供对

存储器阵列和状态寄存器的写保护。有关块保护的说明,请参见表4。

写保护引脚(WP#)

写保护(WP#)引脚用于使能状态寄存器的BPL 位(bit 7)的锁定功能。

当WP# 驱动为低电平时,是否执行写状态寄存器(WRSR)指令由BPL

位的值(见表2)决定。当WP# 为高电平时, BPL 位的锁定功能被禁

止。

状态寄存器

软件状态寄存器提供有关闪存存储器阵列是否可进行任何读或写操作的状态、器

件是否写使能以及存储器写保护的状态。在内部擦除或编程操作期间,可对状态

寄存器只进行读操作,以确定正在进行的操作的完成状态。表3 列出了软件状态

寄存器中每个位的功能。

BUSY

BUSY 位确定是否有内部擦除或编程操作正在进行中。BUSY 位为“1”表示器件正忙

于操作。BUSY位为“0”表示器件准备好进行下一个有效操作。

写使能锁存器(WEL)

写使能锁存器(Write-Enable Latch, WEL)位表示内部寄存器的写使能锁存器

状态。如果写使能锁存器位置“1”,则表示器件写使能。如果该位置“0”(复

位),则表示器件未写使能,并且不接受任何存储器写(编程/ 擦除)命令。在

下列条件下,写使能锁存器位自动复位:

bull; 上电

bull; 写禁止(WRDI)指令完成

bull; 字节编程指令完成

bull; 自动地址递增(AAI)编程完成或达到其最高的不受保护的存储器地址

bull; 扇区擦除指令完成

bull; 块擦除指令完成

bull; 全片擦除指令完成

bull; 写状态寄存器指令

自动地址递增(AAI)

自动地址递增编程状态位提供有关器件处于自动地址递增(Auto Address

Increment, AAI)编程模式还是字节编程模式的状态。上电时默认为字节编程

模式。

块保护(BP3、BP2、BP1 和BP0)

块保护(BP3、BP2、BP1 和BP0)位定义了要通过软件保护方式防止任

何存储器写(编程或擦除)操作的存储器区域的大小,如表4 中定义。只

要WP# 为高电平或块保护锁定(Block-Protect-Lock,BPL)位为0,就可

以使用写状态寄存器(WRSR)指令编程BP3、BP2、BP1 和BP0 位。

仅当块保护位全部为0 时,才能执行全片擦除。上电后, BP3、BP2、BP1

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[149941],资料为PDF文档或Word文档,PDF文档可免费转换为Word

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。