基于多DSP和串行RapidIO互连的高性能计算系统上的数据流量管理案例研究

Abdessamad Klilou,Said Belkouch,Asma Elmaizi,

Philippe Elleaume,Phlippe Le Gall,Franccedil;oisBourzeix,Moha M#39;Rabet Hassani

1摩洛哥先进科学,创新和研究基金会 - MAScIR,摩洛哥拉巴特

2 Ecole Nationale desSciencesAppliqueacute;es-Marrakech,Cadi Ayyad大学,摩洛哥马拉喀什

3 Thales Air Systems,法国巴黎,

a.klilou@mascir.com

摘要 - 本文提出了一种基于Serial- RapidIO(SRIO)互连的大规模并行机。 该机器由多个数字信号处理器(多DSP)和一个多核DSP组成。核心是基本处理单元,SRIO接口是处理器间通信总线。 本文提出的并行机流量管理中的几个案例研究,以便通过管理和控制数据流来做出最佳选择并最大化传输性能。文中给出了每个交通管理和流量控制案例研究的实验结果。

关键词 - 串行RapidIO; 流量控制; 流量管理,多DSP,多核DSP

- 导言

数据传输对计算机的高运算处理能力的要求越来越高以及对高互连总线传输数据的速度要求提高,促使嵌入式行业投入大量资金开发若干高速,低功耗和强大的互连解决方案,并迫使架构师在设计时进行权衡。 最有效的通信架构,适用于特定系统。 RapidIO协议作为一种成功的互连解决方案出现在这种情况下。

RapidIO是一种高性能的分组交换互连技术。 它的开发旨在满足嵌入式行业对更快的总线速度的需求; 增加系统内互连的带宽和可靠性。 RapidIO允许芯片到芯片,板对板和机箱到机箱的通信,性能水平从每通道1Gbps扩展到10 Gbps。

我们已经提出了一种大规模并联机器,以满足脉冲多普勒雷达等应用对高处理能力的需求[1]。 所提出的机器包括作为基本处理元件的多核DSP和作为处理器间通信总线的SRIO。

我们选择多核C6678 DSP作为基本处理元件。 它是一种低功耗,高性能的固定/浮点DSP [2]。 C6678 DSP是一款八核设备; 每个核心可以运行高达1.25 GHz。 它为浮点提供160 GFLOP的峰值性能,对于仅10瓦的固定点提供320 GMAC。 此外,SRIO作为外围设备集成在C6678 DSP中。 本文介绍了一个带有三个C6678 DSP与CPS1848 SRIO交换机互连的实验平台。

本文的目的是研究交通管理的几个案例研究,通过管理和控制所提出的并行机中的数据流来做出最佳选择并最大化传输性能。 给出了每个交通管理和流量控制案例研究的实验结果。

本文的其余部分安排如下。 第2节介绍了使用SRIO研究流量控制和流量管理的相关工作。 第3节概述了RapidIO互连。 第4节描述了拟议的实验平台; 我们概述了C6678 DSP,并介绍了在C6678 DSP中实现的SRIO作为外围设备。 第5节介绍了几种流量管理案例,通过管理和控制所提出的并行机器中的流量,使最佳选择最大化。 最后,第6节提供了结论。

二,相关工作

RapidIO指定物理层和逻辑层的流量控制和流量管理机制。 RapidIO规范1.3中的流量控制旨在通过缓冲数据包和限制发送端点来处理交换机和端点中的瞬态拥塞。 限制机制使用一对XON / XOFF拥塞控制数据包(CCP)分别打开/关闭源。XOFF数据包通常在接收缓冲区超过某个拥塞阈值时生成,并在超过拥塞阈值后发送到其数据包到达队列的所有设备。 一旦队列占用率低于此阈值,接收器就会向所有关闭的设备发送XON消息[3,4]。

Shah等人。 [5]开发了流仲裁协议。 它作为规范1.3的扩展集成到RapidIO 2.0中。 除了XON / XOFF拥塞管理功能外,仲裁协议还添加了以下命令:

- 请求:请求PDU传输的SAR-Context。

- XON-ARB:如果上下文可用,则发送以响应REQ。

- XOFF-ARB:如果没有可用的上下文,则发送。 预计发送者会在一段随机时间后重新发送REQUEST。

- RELEASE:用于表示仅在多PDU情况下完成数据传输。

使用分段和重组(SAR)资源的数据流分配作为示例,发送端点发送单个协议数据单元(PDU)请求。 接收端点将使用XON-ARB或XOFF-ARB消息进行响应,具体取决于它是否具有可用的缓冲区和上下文资源。 如果接收端点以XOFF-ARB响应,则发送端点可以发送新的REQUEST消息以请求资源。 如果接收端点用XON-ARB响应,则发送端点可以开始发送PDU段。

SRIO物理层规范2.1包括四个频点:1.25 Gbps,2.5 Gbps,3.125 Gbps和5Gbps。 这些快速切换信号会产生大量的噪声和辐射,从而降低系统性能并产生电磁干扰(EMI)问题。 物理层流量管理机制旨在处理拥塞时段并确保可靠的数据包传输。 SRIO描述了三种类型的流量管理机制:重试,限制和信用。

Y Zhang等提出了一种新的交通管理方案。 所提出的方案涉及自适应速度转换和冻结确认,以提高SRIO的性能。 自适应速度转换旨在提高系统吞吐量并限制延迟。 冻结确认是为了减少反馈量。

本文介绍了基于多DSP处理器和SRIO互连的嵌入式系统流量管理的几个案例研究。

- RAPIDIO互连概述

RapidIO互连是由RapidIO Trade Association控制的开放标准。 它是一种高性能的分组交换协议,旨在满足嵌入式行业对更快的总线速度,更高的带宽,可靠性,成本效益和可扩展性的需求。 SRIO允许芯片到芯片,板对板和机箱 - 背板通信的性能水平从每链路1 Gbps扩展到10 Gbps。

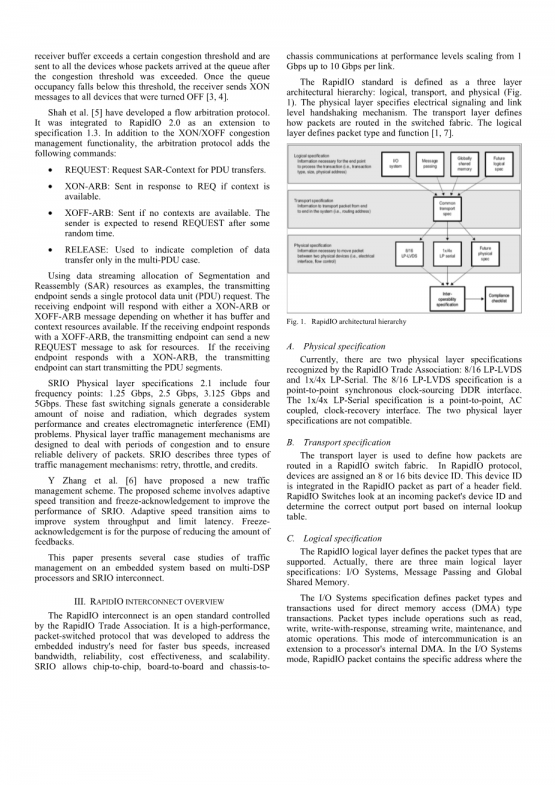

RapidIO标准被定义为三层架构层次结构:逻辑,传输和物理(图1)。 物理层指定电信令和链路级握手机制。 传输层定义了如何在交换结构中路由数据包。 逻辑层定义了数据包类型和函数[1,7]。

图1. RapidIO的架构层次结构

- 物理规格

目前,RapidIO Trade Association认可了两种物理层规格:8/16 LP-LVDS和1x / 4x LP-Serial(一道、两道、四道串行接口)。 8/16 LP-LVDS规范是点对点同步时钟源DDR接口。 1x / 4x LP-Serial规范是一种点对点交流耦合时钟恢复接口。 两个物理层规范不兼容。

- 传送规范

传输层用于定义如何在RapidIO交换机结构中路由数据包。 在RapidIO协议中,为设备分配8或16位设备ID。 此设备ID作为标题字段的一部分集成在RapidIO数据包中。 RapidIO交换机查看传入数据包的设备ID,并根据内部查找表来确定正确的输出端口。

- 逻辑规范

RapidIO逻辑层定义了支持的数据包类型。 实际上,有三种主要的逻辑层规范:I / O系统,消息传递和全局共享存储器。

I / O Systems规范定义了用于直接内存访问(DMA)类型事务的数据包类型和事务。 数据包类型包括诸如读取,写入,写入响应,流写入,维护和原子操作等操作。 这种相互通信模式是处理器内部DMA的扩展。 在I / O系统模式下,RapidIO数据包包含应在目标设备中存储或读取数据的特定地址。 因此,I / O系统模式要求RapidIO源设备为目标设备中的内存保留本地地址表。

消息传递规范实现了数据推送模型,其中始终写入数据。 在此模式下,本地设备接收数据包并将有效负载传输到其内存系统。

RapidIO全局共享内存逻辑层支持缓存一致的非均匀内存访问(CC-NUMA)系统[4]。

- 实验平台描述

本文提出的实验平台通过第二代SRIO开发平台连接的三个多核C6678 DSP芯片组成。

图2.DSP C6678

A.C6678 DSP概述

德州仪器(TI)提供的多核C6678 DSP是基于TI梯形多核架构的低功耗和高性能固定/浮点DSP。 它集成了8个C66x DSP内核(图3)。 每个C66x DSP内核可以运行高达1.25 GHz。 C66x DSP内核基于超长指令字(VLIW)架构。 每个内核运行频率为1 GHz,功耗为10 W. C6678 DSP具有8个以1GHz运行的核心,其峰值性能约为128个单精度GFLOPS(12.8 GFLOPS /瓦特)

片上存储器有三个级别:每个核心具有32KB的1级用于程序(L1P)和32KB的1级用于数据(L1D)。 级别1是最近的,它通常用作缓存。 另外,每个核心具有本地2级存储器; 它比1级慢,大小为512KB。 级别3或MSM(多核共享内存)是共享的,并且由8个内核同时访问; 它的大小是4MB。除此之外,C6678 DSP还可以访问高达8GB的外部DDR3 RAM,每通道高达5Gbps的波特率和两个千兆以太网通道。

图3.C6678的功能框图

B.SRIO在C6678 DSP中实现

通过64位总线。 我们的评测模块EVMC6678包含512Mbytes的DDR3 RAM [2]

C6678 DSP集成了多个高性能外设。 它包含三个DMA,用于在DSP的存储器之间传输数据而不涉及CPU; 它的带宽约为15 GBPS。 它还包含四个高性能互通总线SRIO Gen2通道,每个通道的波特率高达5 Gbps,两个PCIe Gen2通道

C6678 DSP包括SRIO,就像外围设备一样。 它实现了符合RapidIO互连规范REV2.1.1。 支持的物理层符合LP-Serial Specification REV2.1.1; 它使用SerDes技术从数据流中执行时钟恢复,并采用8位/ 10位编码。

C6678 DSP集成了四个SRIO通道。 这些通道可以作为一个4times;端口,两个2times;端口和四个1times;端口运行。 每个1x端口可以以1.25,2.5,3.125和5 Gbps的频率运行。 由于8位/ 10位编码开销,每个差分对的有效数据带宽为1.0,2.0,2.5和4 Gbps。

C6678 DSP实现了RapidIO逻辑层的两种规格I/O系统和消息传递; 全局共享内存未实现。 C6678 DSP中实现的I/O系统模式称为直接I/O. 直接I /O模式支持对RapidIO系统中已知存储空间的基本读写操作。对于直接I/O,RapidIO数据包包含应在目标设备中存储或读取数据的特定地址。

RapidIO目标外设从接收的数据包头中提取目标地址,并通过DMA将有效负载传输到内存。 当CPU想要将数据从存储器发送到外部处理单元(PE)或从外部PE读取数据时,它为SRIO外设提供有关传输的重要信息,如DSP存储器地址,目标器件ID,目标目标地址,数据包 加载/存储单元(LSU)提供了一种机制,通过一组作为传输描述符的存储器映射寄存器(MMR)来处理这种信息交换。 这些寄存器可由CPU寻址。 C6678 DSP包含8个LSU。

作为端点设备,SRIO外围设备根据目标ID接受数据包。 它仅接受目标ID与本地设备ID匹配的数据包。 这提供了一定程度的安全性。 C6678 DSP中的SRIO外设提供15个本地设备ID。 实际上,每个C6678 DSP可以有15个本地设备ID [10]。

根据我们之前的研究工作[1,7],Swrite事务是实现高传输性能的最有效事务。 Swrite事务允许大约90%的SRIO带宽受益。

- 交通管理与流量控制优化

如前所述,所提出的平台包括三个使用4个SRIO链路互连的C6678 DSP。 每个C6678 DSP都有一个带有4个SRIO通道的SRIO端点。 逻辑层提供8个LSU来控制SRIO数据包发送。 每个LSU在所有DSP内核之间共享。 我们已经在两个C6678 DSP之间执行了几种数据传输方案,以便定义最大化数据传输性能的SRIO端口/通道和LSU /核心配置。 所有经验都是使用链路速度为5Gbps的SRIO Swrite事务执行的。

A.场景1:1x,2x和4x端口/通道配置中的数据传输

C6678 DSP集成了四个SRIO通道。 这些通道可以作为一个4x端口,两个2x端口和四个1x端口运行。 我们使用每个端口/通道配置中的Swrite事务测量了两个C6678 DSP之间的数据传输性能。

在1x,2x和4x模式下获得的最大数据速率依次等于3.5 Gbps,6.9 Gbps和12.5 Gbps(图4); 当传输的数据连续大于256字节,1KB和16KB时,它就会到达。

这可以通过以下事实来解释:在1x模式下由SRIO数据包发送的最大有效负载等于256 B.而对于4x模式,SRIO Tx缓冲区最多可以传输16 KB。

总而言之,4x模式是最有效的数据传输性能模式。

图4.使用1X,2X和4X模式的写入事务模式进行数据传输性能

B.场景2:使用2个目标ID进行数据传输

当SRIO端点的输出数据流分布到多个目标SRIO端点时,已提出以下方案来评估数据传输性能。 我们通过为C6678 DSP的一个SRIO端点分配多个本地ID来模拟多个目标端点。

英语原文共 6 页

以上是毕业论文外文翻译,课题毕业论文、任务书、文献综述、开题报告、程序设计、图纸设计等资料可联系客服协助查找。